## 功能描述

ECRF2401 是一款工作在 2.4GHz 世界通用 ISM 頻段的單片集成無線收發晶片。該晶片集成了射頻接收器、射頻發射器、頻率綜合器、GFSK 調製器、GFSK 解調器等功能模組。通過 I2C 介面可以對輸出功率、頻道選擇以及協定進行靈活配置，並且內置 CRC、FEC、自動應答和自動重傳機制，可以大大簡化系統設計並優化性能。週邊電路簡單，只需搭配極少的被動器件就能達到優良的收發性能。

- ◆ 頻率範圍 2402~2530MHz，提供 128 個 channel

- ◆ 無線速率：1Mbps

- ◆ 最大輸出功率 6dBm，靈敏度可達-89dBm

- ◆ 正常配置下（發射功率 6dBm），空曠地帶通信距離大於 80 米

- ◆ I2C 介面

- ◆ 自動回應及自動重傳

- ◆ 快速頻道切換，支援跳頻演算法

- ◆ 支援 RSSI 功能

- ◆ 支援軟體重定

- ◆ 簡單低成本週邊元器件

- ◆ 低工作電壓：1.9V~3.6V

- ◆ SOP8 封裝

- ◆ 當工作在發射模式下（發射功率為 0dBm）時電流消耗為 14mA

- ◆ 當工作在接收模式時電流消耗為 16mA

- ◆ 當工作在休眠模式時電流消耗低於 1uA

## 應用領域

- ◆ 工業感測器及無線工控設備

- ◆ 無線遊戲裝置

- ◆ 遙感勘測

- ◆ 安防系統

- ◆ 智慧運動設備

- ◆ 智慧電視遙控器

- ◆ 無線標籤

- ◆ 無線門禁

- ◆ 安防系統

- ◆ 遙控裝置

- ◆ 無線玩具

## 極限值

| 参数        | 符号      | 最小值  | 最大值 | 单位  |

|-----------|---------|------|-----|-----|

| 工作温度      | Top     | -40  | 100 | °C  |

| 存储温度      | Tstor   | -55  | 125 | °C  |

| 工作电压      | VDD     | -0.3 | 3.7 | V   |

| 输入射频信号强度  | Pin_max |      | +10 | dBm |

| ESD(人体模型) | ESD_HBM |      | 2   | kV  |

## 主要電氣特性

| 特 性                     | 条件(除另有规定外, VCC = 3.3V, TA=25°C) | 参数值  |     |      | 单位   |

|-------------------------|---------------------------------|------|-----|------|------|

|                         |                                 | 最小   | 典型  | 最大   |      |

| <i>ICC</i>              | 休眠模式                            |      | 1   |      | uA   |

|                         | 待机模式                            |      | 1   |      | mA   |

|                         | 发射模式 (0dBm)                     |      | 14  |      | mA   |

|                         | 接收模式                            |      | 16  |      | mA   |

| 系统指标                    |                                 |      |     |      |      |

| <i>f<sub>OP</sub></i>   | 工作频率                            | 2402 |     | 2530 | MHz  |

| <i>f<sub>Xtal</sub></i> | 晶振频率                            |      | 12  |      | MHz  |

| <i>PLL_stable</i>       | PLL 稳定时间                        |      | 150 |      | us   |

|                         | 码率                              |      | 1   |      | Mbps |

| <i>FCH<sub>1M</sub></i> | 频道间隔                            |      | 1   |      | MHz  |

| 发射模式指标                  |                                 |      |     |      |      |

| <i>PRF</i>              | 最大输出功率                          |      | 6   |      | dBm  |

| <i>PRF</i>              | 典型输出功率                          |      | 0   |      | dBm  |

| <i>PRFC</i>             | 输出功率范围                          | -18  |     | 6    | dBm  |

| <i>PBW1</i>             | 载波调制的 20dB 带宽<br>( 1Mbps )      |      | 1   | 1.1  | MHz  |

| 接收模式指标                   |                   |         |     |         |     |

|--------------------------|-------------------|---------|-----|---------|-----|

| <i>RXSENS 2</i>          | 接收灵敏度 ( 0.1%BER ) |         | -89 |         | dBm |

| 抗干扰特性                    |                   |         |     |         |     |

| <i>C/I<sub>CO</sub></i>  | 同道干扰              |         | 9   |         | dBc |

| <i>C/I<sub>1ST</sub></i> | 第 1 相邻道干扰         |         | 5   |         | dBc |

| <i>C/I<sub>2ND</sub></i> | 第 2 相邻道干扰         |         | -12 |         | dBc |

| <i>C/I<sub>3RD</sub></i> | 第 3 相邻道干扰         |         | -24 |         | dBc |

| 操作条件                     |                   |         |     |         |     |

| <i>VDD</i>               | 供电电压              | 1.9     | 3   | 3.6     | V   |

| <i>VSS</i>               | 芯片地               |         | 0   |         | V   |

| <i>V<sub>OH</sub></i>    | 高电平输出电压           | VDD-0.3 |     | VDD     | V   |

| <i>V<sub>OL</sub></i>    | 低电平输出电压           | VSS     |     | VSS+0.3 | V   |

| <i>V<sub>IH</sub></i>    | 高电平输入电压           | 2.0     | 3   | 3.6     | V   |

| <i>V<sub>IL</sub></i>    | 低电平输入电压           | VSS     |     | VSS+0.3 | V   |

| <i>Cin</i>               | 输入电容              |         |     | 10      | pF  |

|                          | 工作温度              | -40     | 27  | +100    | °C  |

|                          | 储存温度              | -40     | 27  | +125    | °C  |

Notes: 12MHz 晶振的负载电容为22pF

## 品名定義

### ECRF2401 XX R

封裝型態：

M1 : SOP8

## 引腳說明

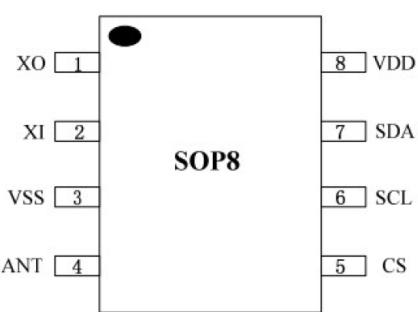

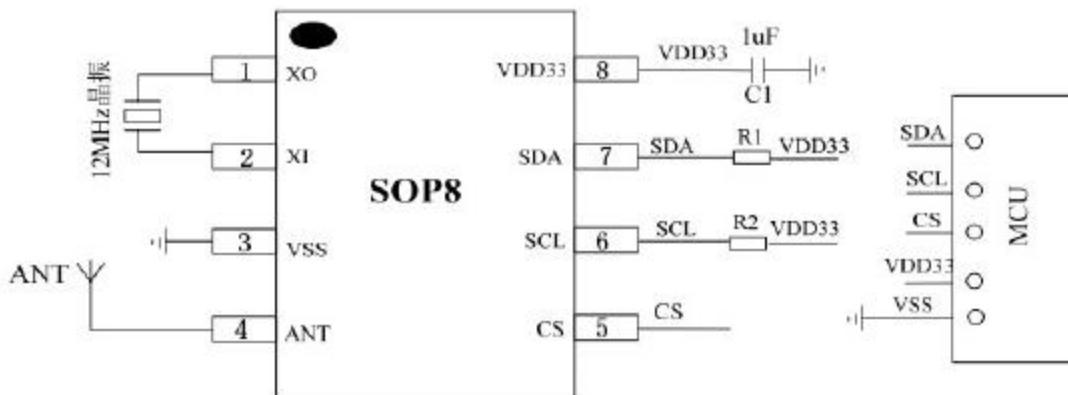

| 序号 | Pin Name | Type  | Description                  |

|----|----------|-------|------------------------------|

| 1  | XO       | AO    | 晶体振荡器输出                      |

| 2  | XI       | AI    | 晶体振荡器输入                      |

| 3  | VSS      | GND   | 地                            |

| 4  | ANT      | RF I  | 射频输入                         |

| 5  | CS       | DI    | 使能信号，低有效，拉低可使芯片退出 sleep mode |

| 6  | SCL      | DI    | I2C 时钟输入脚                    |

| 7  | SDA      | D I/O | I2C 数据脚                      |

| 8  | VDD33    | PWR   | 3.3V 电源出入                    |

## I2C 介面說明

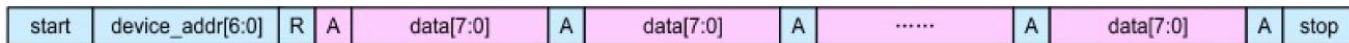

### A. I2C 命令格式

Master 寫一個或多個位元組到 FIFO 或 Register

Master 寫一個位元組到指定的寄存器，然後從 FIFO 中讀出 1 個或多個位元組資料

Master 可以連續讀出 FIFO 資料

Sr: Repeated Start

A: Acknowledge

Master to Slave

Slave to Master

### B. I2C 特性

| I2C 设备从模式可选特性               | 是否支持 |

|-----------------------------|------|

| Standard mode – 100 kbps    | Yes  |

| Fast mode – 400 kbps        | Yes  |

| Fast mode plus – 1000 kbps  | Yes  |

| High speed mode – 3200 kbps | No   |

| Clock stretching            | No   |

| 10-bit slave address        | No   |

| General call address        | No   |

| Software reset              | No   |

| Device id                   | No   |

**C. I2C 器件地址**

| A6 | A5 | A4 | A3 | A2 | A1 | A0 | R/W               |

|----|----|----|----|----|----|----|-------------------|

| 0  | 1  | 1  | 1  | 0  | 0  | 0  | Read=1<br>Write=0 |

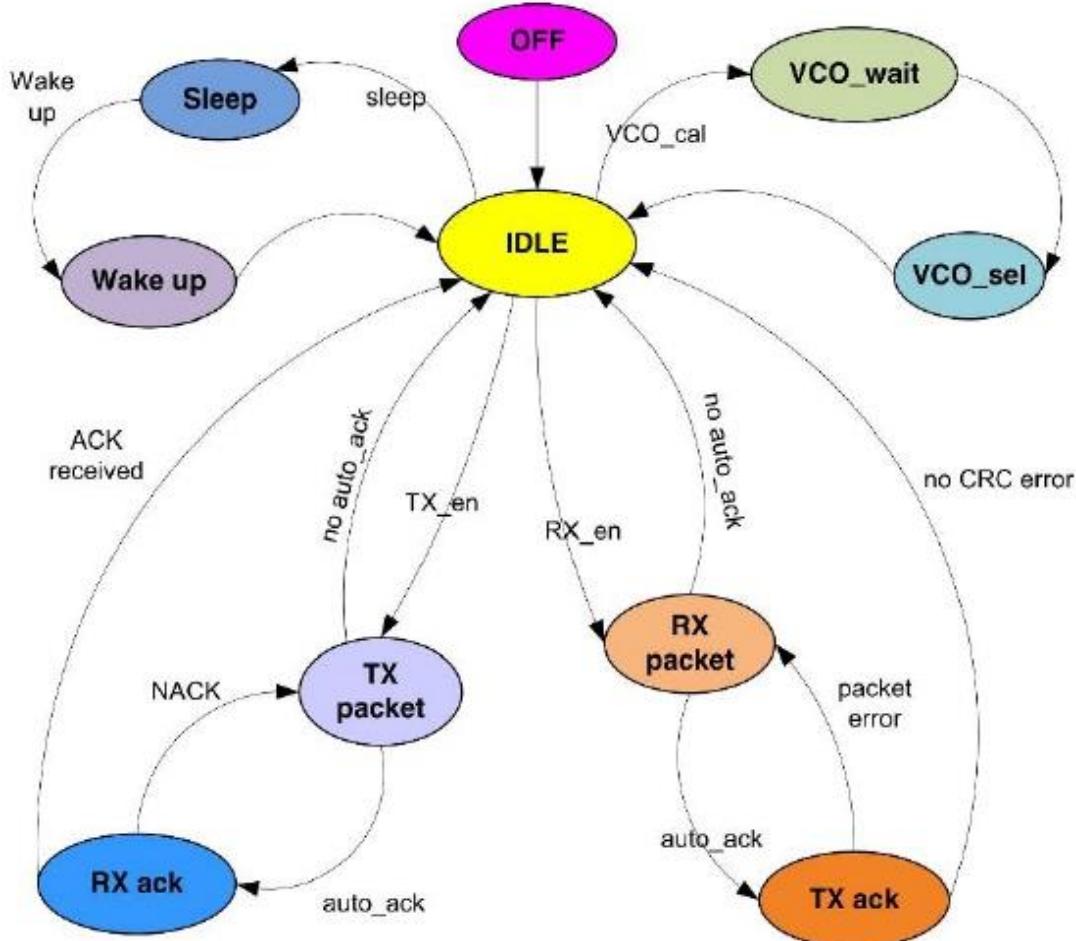

**狀態控制圖**

**寄存器說明**

**RF Synthesizer TX/RX control Register 0x00 default : 0x0030**

| Bit   | Name              | R/W | Description                                       | Default |

|-------|-------------------|-----|---------------------------------------------------|---------|

| 15    | TX_EN             | R/W | 1: Enable transmit sequence                       | 0       |

| 14    | RX_EN             | R/W | 1: Enable receive sequence                        | 0       |

| 13-12 | reserved          | R/W |                                                   | 00      |

| 11-7  | SWALLOW[4:0]      | R/W | When RF_PLL_DIRECT=1<br>RF={reg0[6:0],reg0[13:9]} | 00000   |

| 6-0   | RF_PLL_CH_NO[6:0] | R/W | When RF_PLL_DIRECT=0<br>RF=2402+RF_PLL_CH_NO[6:0] | f=2450  |

**Miscellaneous configuration Register 0x01 default: 0x2077**

| Bit | Name            | R/W | Description                                                                                                            | Default |

|-----|-----------------|-----|------------------------------------------------------------------------------------------------------------------------|---------|

| 15  | Sleep_mode      | R/W | 1: enter deep sleep mode                                                                                               | 0       |

| 14  | brclk_on_sleep  | R/W | 1: oscillator run in sleep mode, more current but fast wakeup<br>0: oscillator stop in sleep mode                      | 0       |

| 13  | CRC_EN          | R/W | 0: CRC off 1: CRC on                                                                                                   | 1       |

| 12  |                 |     |                                                                                                                        |         |

| 11  |                 |     |                                                                                                                        |         |

| 10  | RF_PLL_DIRECT   | R/W | When RF_PLL_DIRECT=1<br>RF={reg0[6:0],reg0[13:9]}<br>otherwise<br>RF=2402+RF_PLL_CH_NO[6:0]                            | 0       |

| 9   | Pkt_hint_parity | R/W | 1: PKT/FIFO flag low active<br>0: PKT/FIFO flag high active                                                            | 0       |

| 8   | Miso_tri_opt    | R/W | 0: SPI_MISO is tri_state when SPI_CS=1<br>1: SPI_MISO is low when SPI_CS=1                                             | 0       |

| 7   | Reset_system    | W/R | Reset system, write 1'b1 to reset all digital block                                                                    | 0       |

| 6-4 |                 |     |                                                                                                                        |         |

| 3   | Auto-ack        | R/W | 1: after received data, automatically send ACK<br>0: after received data, do not send ACK, just enter IDLE             | 0       |

| 2   | Pack_lenth_en   | R/W | 1: Hardware regard first byte of payload as packet length                                                              | 1       |

| 1   | Fw_term_tx      | R/W | 0: Firmware handle length and terminate TX by MCU<br>1: when fifo write point equals read point, hardware terminate TX | 1       |

| 0   | SCRAMBLE_EN     | R/W | 0: scramble off 1: scramble on                                                                                         | 1       |

**PA Power Control Register 0x02 default: 0x3080**

| Bit   | Name           | R/W | Description                                                                         | Default |

|-------|----------------|-----|-------------------------------------------------------------------------------------|---------|

| 15-12 | reserved       | R/W |                                                                                     | 0011    |

| 11-8  | reserved       | R/W | rev                                                                                 | 0000    |

| 7-4   | reserved       | R/W |                                                                                     | 1000    |

| 3-0   | PA_PW_SET[4:0] | R/W | PA Power set, reg[10:7] is a unsigned number<br>1111: min<br>1000: med<br>0000: max | 0000    |

**Operation configuration Register 0x03 default: 0x5800**

| Bit   | Name                  | R/W | Description                                                                                                                                                                                                    | Default |

|-------|-----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 15-13 | Preamble_len[2:0]     | R/W | 000: 1 byte, 10101010<br>001: 2 byte, 10101010 10101010<br>111: 8 byte, 10101010.....                                                                                                                          | 010     |

| 12-11 | Syncword_len[1:0]     | R/W | 00: 16 bits, {reg31[15:0]}<br>01: 32 bits, {reg31[15:0],<br>reg34[15:0]}<br>10: 48 bits, {reg31[15:0],<br>reg33[15:0], reg34[15:0]}<br>11: 64 bits, {reg31[15:0],<br>reg32[15:0], reg33[15:0],<br>reg34[15:0]} | 11      |

| 10-8  | Trailer_len[2:0]      | R/W | 000: 4 bits, 1010<br>001: 6 bits, 101010<br>.....<br>111: 18 bits, 101010.....101010                                                                                                                           | 000     |

| 7-6   | Data packet type[1:0] | R/W | 00: NRZ low data<br>01: Manchester data type<br>10: 8/10 line code<br>11: interleave data type                                                                                                                 | 00      |

| 5-4   | FEC type[1:0]         | R/W | 00: No FEC<br>01: FEC 13<br>10: FEC 23<br>11: reserve, same as 00                                                                                                                                              | 00      |

| 3     |                       |     |                                                                                                                                                                                                                |         |

|     |                |     |                                                                                                                                                            |     |

|-----|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2-0 | brelk_sel[2:0] | R/W | 000: brelk keep 0<br>001: xtal_corc out<br>010: crystal divided by 6, 2M out<br>011: crystal divided by 12, 1M out<br>100: APLL_clk out<br>101: clk_tx_out | 000 |

|-----|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

**Operating configuration Register 0x07 default: 0x7311**

| Bit   | Name              | R/W | Description                                                                                                | Default |

|-------|-------------------|-----|------------------------------------------------------------------------------------------------------------|---------|

| 15    | EN_VCO_CAL_IDLE   | R/W | 1: manually enable VCO calibration during IDLE                                                             | 0       |

| 14    | TXRX_VCO_CAL_EN   | R/W | 1: enable TX/RX VCO calibration                                                                            | 1       |

| 13-10 | TXRX_vco_tim[3:0] | R/W | TXRX vco calibration waiting time,base is 6us, 1 step 2us<br>0000: 6us<br>0001: 8us<br>.....<br>1111: 36us | 1100    |

| 9-0   |                   |     |                                                                                                            |         |

**Timing configuration Register 0x0b default: 0x837F**

| Bit   | Name             | R/W | Description                                                                          | Default |

|-------|------------------|-----|--------------------------------------------------------------------------------------|---------|

| 15-12 | TX_CW_DLY[3:0]   | R/W | Transmit CW after PA ON,2us base, 2us step<br>0000: 2us<br>0001: 4us<br>1111: 32us   | 1000    |

| 11-8  | Re_transmit_time | R/W | Max re_transmit packet times when auto ACK on<br>2H: 2 times<br>3H: 3 times<br>..... | 0011    |

|     |                   |     |                                                                            |        |

|-----|-------------------|-----|----------------------------------------------------------------------------|--------|

| 7-6 | Wake_up_time[1:0] | R/W | Wake up time, base 4us, step 4us<br>00: 4us<br>01: 8us<br>...<br>11: 16us  | 01     |

| 5-0 | Rx_ack_time[5:0]  | R/W | Wait RX_ack ID timer setting,<br>step is 16us<br>T=16us x Rx_ack_time[5:0] | 111111 |

**Timing configuration Register 0x0c default: 0x3E11**

| Bit   | Name                | R/W | Description                                                                                                            | Default |

|-------|---------------------|-----|------------------------------------------------------------------------------------------------------------------------|---------|

| 15-10 | VCO_ON_DLY[5:0]     | R/W | After set TX or RX, wait delay timer for VCO setting, 4us step<br>000000: 4us<br>000001: 8us<br>.....<br>111111: 256us | 001111  |

| 9-8   | TX_PA_OFF_DLY[1:0]  | R/W | Delay timer for setting PA OFF after PA_OFF command, 4us base, 2us step<br>00: 4us<br>01: 6us<br>10: 8us<br>11: 10us   | 10      |

| 7-4   | TX_PA_ON_DLY[3:0]   | R/W | waite delay timer for PA fully on after VCO_ON, 4us step<br>x000: 4us<br>x001: 8us<br>...<br>x1111: 32us               | 0001    |

| 3-0   | TX_SW_ON_DELAY[3:0] | R/W | waite delay timer for TX_SW on after VCO_ON, 4us step<br>0000: 4us<br>0001: 8us<br>...<br>11111: 64us                  | 0001    |

**RSSI value Register 0x11 Read only**

| Bit  | Name          | R | Description                          | Default |

|------|---------------|---|--------------------------------------|---------|

| 15-8 | RAW_RSSI[7:0] | R | 8 bit RSSI value from analog circuit |         |

| 7-0  | rss1_lat[7:0] | R | RSSI latch                           |         |

**Block status Register 0x12 Read only**

| Bit   | Name          | R | Description                            | Default | Optium |

|-------|---------------|---|----------------------------------------|---------|--------|

| 15-14 |               |   |                                        |         |        |

| 13    | FIFO_FLAG     | R | 1: FIFO empty or full                  |         |        |

| 12    | reserved      | R |                                        |         |        |

| 11    |               |   |                                        |         |        |

| 10    | VCO_CAL_ERROR | R | Indicates no proper VCO curve selected |         |        |

| 9-0   |               |   |                                        |         |        |

**Main status Register 0x16 Read only**

| Bit  | Name         | R | Description                                                                                               | Default | Optium |

|------|--------------|---|-----------------------------------------------------------------------------------------------------------|---------|--------|

| 15   | Crc_error    | R | 1: Receive CRC error                                                                                      |         |        |

| 14   | FEC23_error  | R | 1: Indicate FEC23 error                                                                                   |         |        |

| 13-8 | Framer_st    | R | Framer status<br>31H: ST_SLEEP<br>33H: ST_WAKE_UP.....<br>.....                                           |         |        |

| 7    | Syneword_rev | R | 1: syneword received                                                                                      |         |        |

| 6    | PKT_FLAG     | R | Packet flag indicator                                                                                     |         |        |

| 5-3  | Tx_st[2:0]   | R | Transmit packet control state<br>000: TX_IDLE<br>001:TX_ID<br>010: TX_CRC<br>011: TX_DATA<br>110: TX_DONE |         |        |

| 2-0  | Rx_st[2:0]   | R | Receive packet control state<br>000: RX_IDLE<br>001:RX_ID<br>010: RX_DATA                                 |         |        |

|  |  |  |                                                |  |  |

|--|--|--|------------------------------------------------|--|--|

|  |  |  | 011: RX_TRAILER<br>100: RX_DONE<br>110: RX_CRC |  |  |

|--|--|--|------------------------------------------------|--|--|

**AMS TEST Control Register 0x1c default: 0x4008**

| Bit | Name         | R/W | Description                                       | Default | Optim |

|-----|--------------|-----|---------------------------------------------------|---------|-------|

| 15  | RSSI_PDN     | R/W | 1: force power down RSSI                          | 0       |       |

| 14  | SENSOR_EN    | R/W | 1: temperature sense enable                       | 1       |       |

| 13  | Bg_tst_pdn   | R/W | 1: BG power down during AMS_TST_ENB=1             | 0       |       |

| 12  | Xtal_tst_pdn | R/W | 1: crystal buffer power down during AMS_TST_ENB=1 | 0       |       |

| 11  | RSSI_DIS     | R/W | 1: disable RSSI clock                             | 0       |       |

| 10  | cw_mode      | R/W | 1: cw mode 0: normal mode                         | 0       |       |

| 9   | TEST1_OUT_EN | R/W | 1: select TEST1 pin as SYNTH_SIGOUT output        | 0       |       |

| 8   | TEST_DIV     | R/W | 1: route "DIV" signal as SYNTH_SIGOUT output      | 0       |       |

| 7   | TEST_FREF    | R/W | 1: route "FREF" signal as SYNTH_SIGOUT output     | 0       |       |

| 6   | TEST_NA      | R/W | 1: route "NA" signal as SYNTH_SIGOUT output       | 0       |       |

| 5   | reserved     | R/W |                                                   | 0       |       |

| 4   | ADC_DATA_OUT | R/W | 1: 8 bit ADC word and clock mux out at test mode  | 0       |       |

| 3   | AMS_BUF_PD   | R/W | 1: power down test buffer                         | 1       |       |

| 2   | AMS_BUF_LS   | R/W | 1: enable level shift of test buffer              | 0       |       |

| 1   | AMS_BUF_GN   | R/W | Gain control for test buffer                      | 0       |       |

| 0   | AMS_BUF_SIN  | R/W | 1: Single-end input for test buffer               | 0       |       |

**AMS TEST Control Register 0x1c default: 0x7FF4**

| Bit | Name           | R/W | Description                                              | Default | Optimum |

|-----|----------------|-----|----------------------------------------------------------|---------|---------|

| 15  | AMS_TST_ENB    | R/W | 1: enable the AMS test mode and bypass the state machine | 0       |         |

| 14  | APLL_BG_TST_PD | R/W | 1: BG&APLL power down during AMS_TST_ENB=1               | 1       |         |

|    |               |     |                                                                     |   |  |

|----|---------------|-----|---------------------------------------------------------------------|---|--|

| 13 | RF_VCO_TST_PD | R/W | 1: RF_VCO power down during AMS_TST_ENB=1                           | 1 |  |

| 12 | SYNTH_TST_PD  | R/W | 1:SYNTH power down during AMS_TST_ENB=1                             | 1 |  |

| 11 | TXDAC_TST_PD  | R/W | 1: TXDAC power down during AMS_TST_ENB=1                            | 1 |  |

| 10 | TX_PA_TST_PD  | R/W | 1: PA power down during AMS_TST_ENB=1                               | 1 |  |

| 9  | LNA_TST_PD    | R/W | 1: LNA power down during AMS_TST_ENB=1                              | 1 |  |

| 8  | MIXER_TST_PD  | R/W | 1: MIXER power down during AMS_TST_ENB=1                            | 1 |  |

| 7  | BPF_TST_PD    | R/W | 1: BPF power down during AMS_TST_ENB=1                              | 1 |  |

| 6  | RC_TST_PD     | R/W | 1: RC-CAL power down during AMS_TST_ENB=1                           | 1 |  |

| 5  | ADC_TST_PD    | R/W | 1: ADC power down during AMS_TST_ENB=1                              | 1 |  |

| 4  | RC_TST_START  | R/W | 1: Provide test value for RC start during AMS_TST_ENB=1             | 1 |  |

| 3  | ADC_TST_CLKEN | R/W | 1: Enable ADC clock during AMS_TST_ENB=1                            | 0 |  |

| 2  | TR_TST_SW     | R/W | SW control during AMS_TST_ENB=1, 1: TX 0: RX                        | 1 |  |

| 1  | TXDAC_MOD_MON | R/W | 1:enable ADC output monitor                                         | 0 |  |

| 0  | REG_RESET_EN  | R/W | 1:enable write register to reset (enable system reset, high active) | 0 |  |

**SYN\_WORD\_1 Register 0x1f default: 0x0101**

| Bit  | Name            | R/W | Description                   | Default |

|------|-----------------|-----|-------------------------------|---------|

| 15-0 | SYNC_WORD[15:0] | R/W | LSB bits of SYN_WORD is first | 0101H   |

**SYN\_WORD\_2 Register 0x20 default: 0x0202**

| Bit  | Name             | R/W | Description                   | Default |

|------|------------------|-----|-------------------------------|---------|

| 15-0 | SYNC_WORD[31:16] | R/W | LSB bits of SYN_WORD is first | 0202H   |

**SYN\_WORD\_3 Register 0x21 default: 0x0303**

| Bit  | Name             | R/W | Description                   | Default |

|------|------------------|-----|-------------------------------|---------|

| 15-0 | SYNC_WORD[47:32] | R/W | LSB bits of SYN_WORD is first | 0303H   |

**SYN\_WORD\_4 Register 0x22 default: 0x0404**

| Bit  | Name             | R/W | Description                   | Default |

|------|------------------|-----|-------------------------------|---------|

| 15-0 | SYNC_WORD[63:48] | R/W | LSB bits of SYN_WORD is first | 0404H   |

**Register 0x23 default: 0x8001**

| Bit  | Name          | R/W | Description         | Default |

|------|---------------|-----|---------------------|---------|

| 15   | FIFO_share_en | R/W | 1: share RX/TX FIFO | 0       |

| 14:0 |               |     |                     |         |

**FIFO threshold\_reg Register 0x24 default: 0x4401**

| Bit   | Name                 | R/W | Description                       | Default |

|-------|----------------------|-----|-----------------------------------|---------|

| 15-11 | FIFO_empty_threshold | R/W | FIFO empty byte threshold at TX   | 01000   |

| 10-6  | FIFO_full_threshold  | R/W | FIFO full byte threshold at RX    | 10000   |

| 5-0   | Synword_threshold    | R/W | ID correction Error bit threshold | 000001  |

**RX\_FIFO\_RD\_PTR Register 0x25 default: 0x0000**

| Bit  | Name                | R/W | Description                                      | Default |

|------|---------------------|-----|--------------------------------------------------|---------|

| 15   | RXFIFO_CLR_W_PTR    | R/W | 1: Clear RX FIFO point to 0 ,not available in RX | 0       |

| 14   | RX_FIFO_WR_PTR[6]   | R/W | available at fifo_share_en=1                     | 0       |

| 13-8 | RX_FIFO_WR_PTR[5:0] | R/W | FIFO write point                                 | 0       |

| 7    | RXFIFO_CLR_R_PTR    | R/W | 1: Clear RX FIFO point to 0, not available in RX | 0       |

| 6    | RX_FIFO_RD_PTR[6]   | R/W | available at fifo_share_en=1                     | 0       |

| 5-0  | RX_FIFO_RD_PTR[5:0] | R/W | FIFO read point                                  | 0H      |

**TX\_FIFO\_RD\_PTR Register 0x26 default: 0x0000**

| Bit  | Name                | R/W | Description                                      | Default |

|------|---------------------|-----|--------------------------------------------------|---------|

| 15   | TXFIFO_CLR_W_PTR    | R/W | 1: Clear TX FIFO point to 0 ,not available in TX | 0       |

| 14   | TX_FIFO_WR_PTR[6]   | R/W | available at fifo_share_en=1                     | 0       |

| 13-8 | TX_FIFO_WR_PTR[5:0] | R/W | FIFO write point                                 | 0       |

|     |                     |     |                                                  |    |

|-----|---------------------|-----|--------------------------------------------------|----|

| 7   | TXFIFO_CLR_R_PTR    | R/W | 1: Clear TX FIFO point to 0, not available in TX | 0  |

| 6   | TX_FIFO_RD_PTR[6]   | R/W | available at fifo_share_en=1                     | 0  |

| 5-0 | TX_FIFO_RD_PTR[5:0] | R/W | FIFO read point                                  | 0H |

**TX\_FIFO\_REG Register 0x27 default: 0x0000**

| Bit  | Name        | R/W | Description                              | Default |

|------|-------------|-----|------------------------------------------|---------|

| 15-0 | TX_FIFO_REG | R/W | For mcu read/write data between the FIFO | 0000H   |

**RX\_FIFO\_REG Register 0x28 default: 0x0000**

| Bit  | Name        | R/W | Description                              | Default |

|------|-------------|-----|------------------------------------------|---------|

| 15-0 | RX_FIFO_REG | R/W | for mcu read/write data between the FIFO | 0000H   |

### 寄存器默認值及優化值

晶片共有 42 個寄存器，復位後，所有寄存器均為預設值，如表 A 所示。正常工作時，只需要對少數幾個寄存器的值進行優化即可，如表 B 所示。

表 A

| Address | reset value | Address | reset value |

|---------|-------------|---------|-------------|

| 0x00    | 0x0030      | 0x15    | Read only   |

| 0x01    | 0x2077      | 0x16    | Read only   |

| 0x02    | 0x3080      | 0x17    | 0x0000      |

| 0x03    | 0x5800      | 0x18    | 0x6FE1      |

| 0x04    | 0x4A00      | 0x19    | 0x1300      |

| 0x05    | 0x7126      | 0x1a    | 0x07F7      |

| 0x06    | 0x1988      | 0x1b    | 0x1800      |

| 0x07    | 0x7311      | 0x1c    | 0x4008      |

| 0x08    | 0x1659      | 0x1d    | 0x0000      |

| 0x09    | 0x007B      | 0x1e    | 0x7FF4      |

| 0x0a    | 0x2433      | 0x1f    | 0x0101      |

| 0x0b    | 0x837F      | 0x20    | 0x0202      |

| 0x0c    | 0x3E11      | 0x21    | 0x0303      |

| 0x0d    | 0x6000      | 0x22    | 0x0404      |

| 0x0e    | 0x4c00      | 0x23    | 0x8001      |

| 0x0f    | 0x6609      | 0x24    | 0x4401      |

| 0x10    | 0x5F8F      | 0x25    | 0x0000      |

| 0x11    | Read only   | 0x26    | 0x0000      |

| 0x12    | Read only   | 0x27    | 0x0000      |

| 0x13    | Read only   | 0x28    | 0x0000      |

| 0x14    | Read only   | 0x29    | 0x0000      |

表 B

| Address | Opt value |

|---------|-----------|

| 0x0a    | 0x2053    |

| 0x02    | 0x4060    |

| 0x05    | 0x7fa6    |

| 0x0f    | 0x661d    |

| 0x0d    | 0x6003    |

| 0x1a    | 0x00f7    |

## 應用線路

注：晶片內部已經在 SDA 和 SCL 腳上各集成了 4.7K 的上拉電阻，在一般應用場合中，外部上拉電阻 R1 和 R2 可不加。

## 注意事項

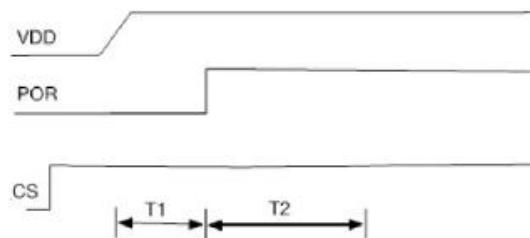

### 上電和寄存器初始化資料

1. 晶片內部集成上電重定功能 (POR)，T1 時間為上電復位時間，約 0.5ms

2. T2 是晶振穩定時間，約為 1.5ms，然後由 MCU 初始化寄存器

3. 寄存器初始化完成後，晶片可以開始發射或接收資料

4. 除了內部自動重定，晶片還有軟體重定功能：

a、軟體重定：先寫 0x1e[0]寄存器為‘1’，使能軟體重定功能，再對 0x01[7]寄存器寫‘1’就可以完成復位操作。

## 進入 sleep mode 和喚醒

當 CS 拉高，並且 MCU 寫寄存器 0x01[15]為“1”後，晶片進入 sleep mode，此時消耗電流<1uA,sleep mode 下寄存器的值能夠保持。當 CS 拉低後，晶片自動喚醒進入 IDLE 狀態。MCU 要拉低 CS 一段時間(等待晶體穩定，約 1.5ms)，再讀寫資料。

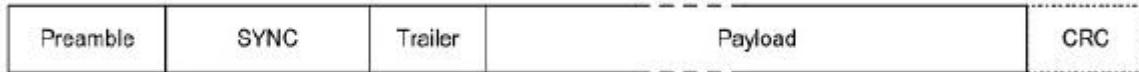

## 資料包格式

空中資料包格式

- ◆ Preamble: 1~8 bytes, programmable.

- ◆ SYNC: 16/32/48/64 bits, programmable as device syncword.

- ◆ Trailer: 4~18 bits, programmable.

- ◆ Payload: TX/RX data. There are 4 data types:

- Raw data

- 8bit/10bitlinecode

- Manchester

- Interleave with FEC option

- ◆ CRC: 16-bit CRC is optional.

## FIFO 長度

預設是 64 個位元組，接收和發送共用，也可設置成分開使用各 32 個位元組把 0x23[15]設置為 0 即各使用 32 位元組

## 清空 FIFO 指針

1. 接收 FIFO 和發送 FIFO 的讀寫指針都可通過對 0x25, 0x26 相應寄存器寫‘1’來清除

2. 當接收到資料包，讀指標將指示 FIFO 中有多少 bytes 數據。

3. 當接收器收到 SYNC 時，接收 FIFO 寫指針會自動清 0。

4. 當發射器發送完資料後，發射 FIFO 讀指針會自動清 0。

## 數據包 payload 長度

兩種方式去確定 TX/RX 包長度。當寄存器 0x01[2]=1 時，內部狀態機會根據 payload 第一個 byte 資料來檢測包長度。如要發 8 個 byte，第一個 byte 應寫 8，總字長為 9 個 byte。

當寄存器 0x01[2]=0，第一個 byte 資料沒什麼特殊意義。資料包長度將由 TX FIFO 何時為空或者何時清空 TX\_EN 來決定，見下表。

| 0x01[2]<br>pack_length_en | 0x01[1]<br>fw_term_tx |                                                             |

|---------------------------|-----------------------|-------------------------------------------------------------|

| 0                         | 0                     | 當TX_EN=0 時，終止發射。<br>當RX_EN=0 時，終止接收。                        |

|                           | 1                     | 當 FIFO 為空時，自動終止發射。<br>當RX_EN=0 時，終止接收。                      |

| 1                         | x                     | Payload 第一個位元組表示包長度 0 到 255bytes。當發完 0 到 255bytes 後，發射自動終止。 |

## 狀態機決定包長度

當寄存器 0x01[2]=1 時，payload 的第一個 byte 表示包長度，最大長度是 255 bytes。

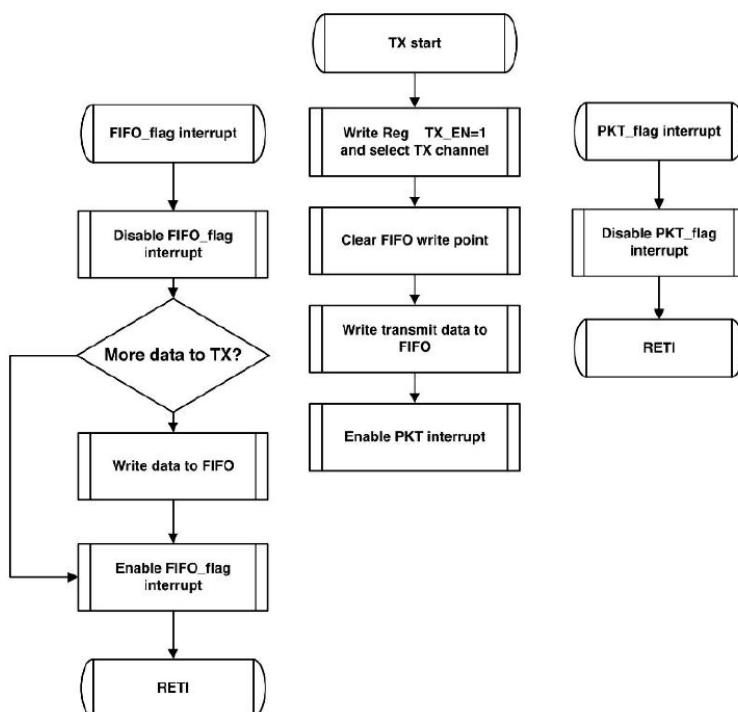

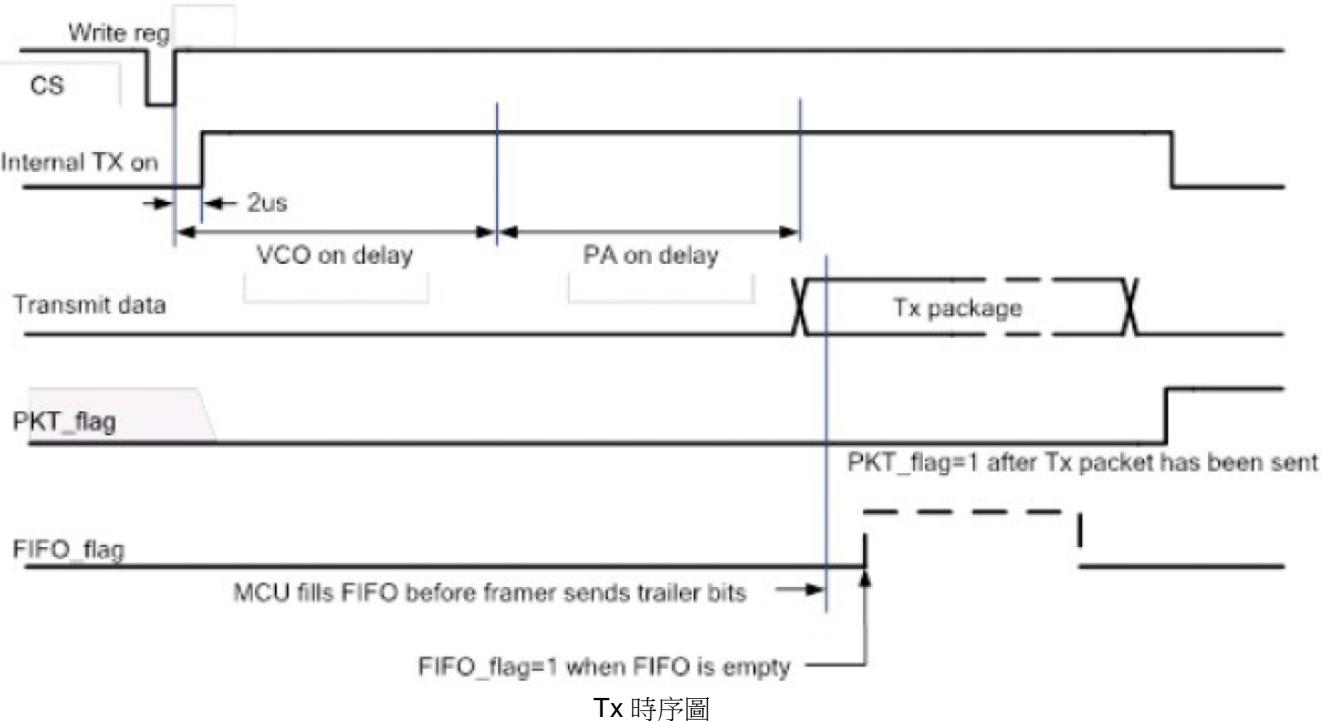

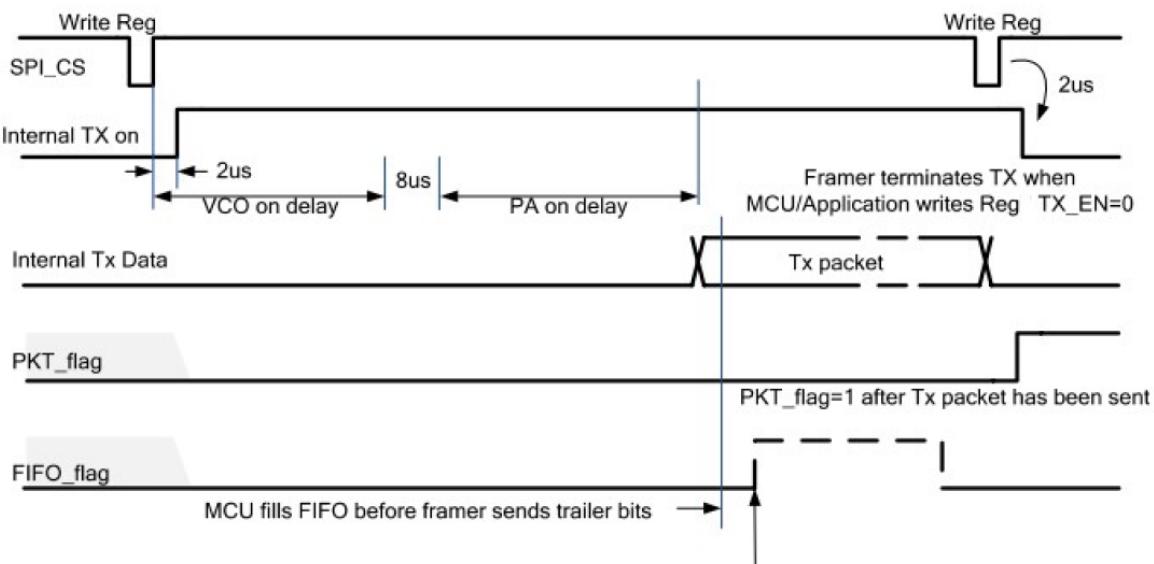

### ◆發射時序

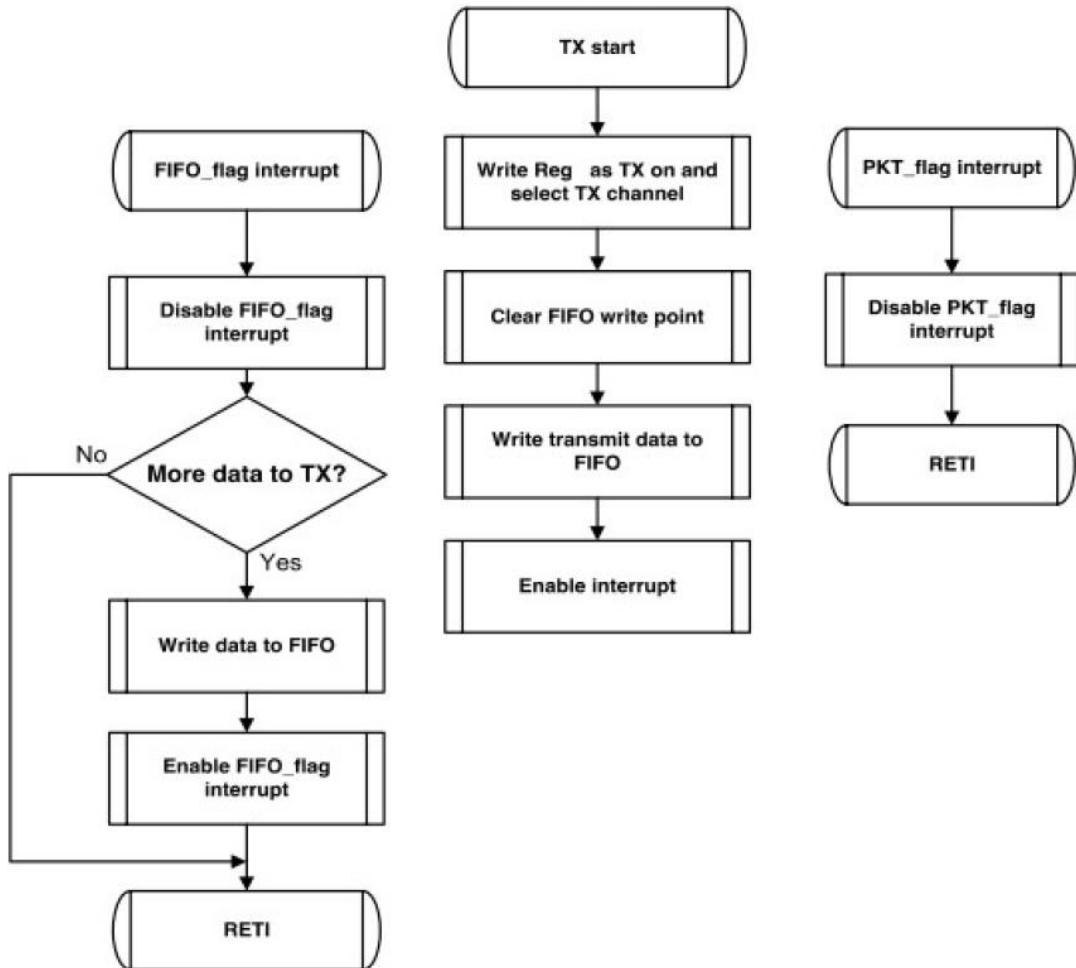

下面顯示 TX 時序.：當 MCU 將寄存器 0x00[15]寫為‘1’後，同時寫寄存器 0x00[6:0]設定好發射通道，晶片將自動根據 payload 來產生包。MCU 需要在發射 trailer 前寫入發射數據。如果包長度超過 FIFO 長度，MCU 需要多次寫 FIFO 資料。FIFO flag(reg0x12[13])表示 FIFO 是不是為空。

MCU 發送資料包流程圖

FIFO 和 PKT flags 作為 MCU 的中斷信號

在上面的流程圖中，先使能發送狀態機，再寫發送資料到發送 FIFO 中，這樣可以提高 MCU 效率，但要保證資料包在發送 TRAILER 之前寫入所有資料；如果要寫入的時間需要很長，則應先寫好所有資料再啟動發送狀態。

////////// 發射流程例子：

1. 初始化寄存器，即寫入需要優化的寄存器值

```

write reg[0x0a] = 0x2053;

write reg[0x02] = 0x4060;

write reg[0x05] = 0x7fa6;

write reg[0x0f] = 0x661d;

write reg[0x0d] = 0x6003;

write reg[0x1a] = 0x00f7;

```

2. 清空發送 FIFO

```

write reg[0x26] = 0x8080;

```

3. 寫資料到 FIFO，發送資料：0x05 0x01 0x02 0x03 0x04 0x05,第一個位元組表示長度

```

write reg[0x27] = 0x0501;

write reg[0x27] = 0x0203;

write reg[0x27] = 0x0405;

```

4. 啟動發送使能，同時設置頻道

```

write reg[0x00] = 0x80XX; //低 7 位元為頻道號

```

5. 等待 pkt\_flag(reg0x16[6])為高，表示發送完成

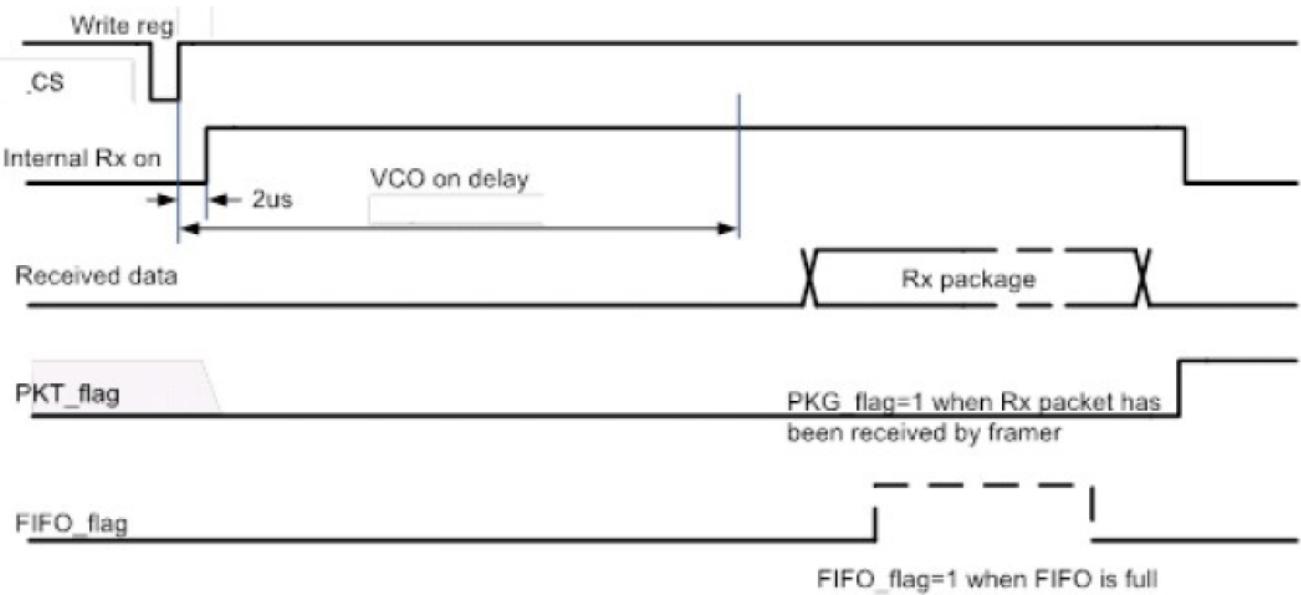

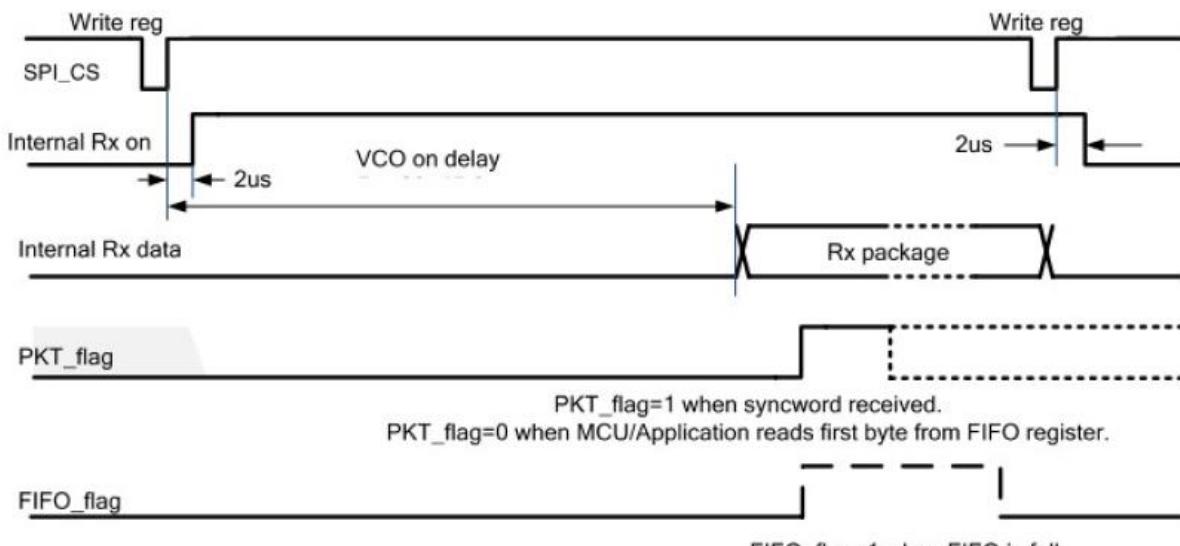

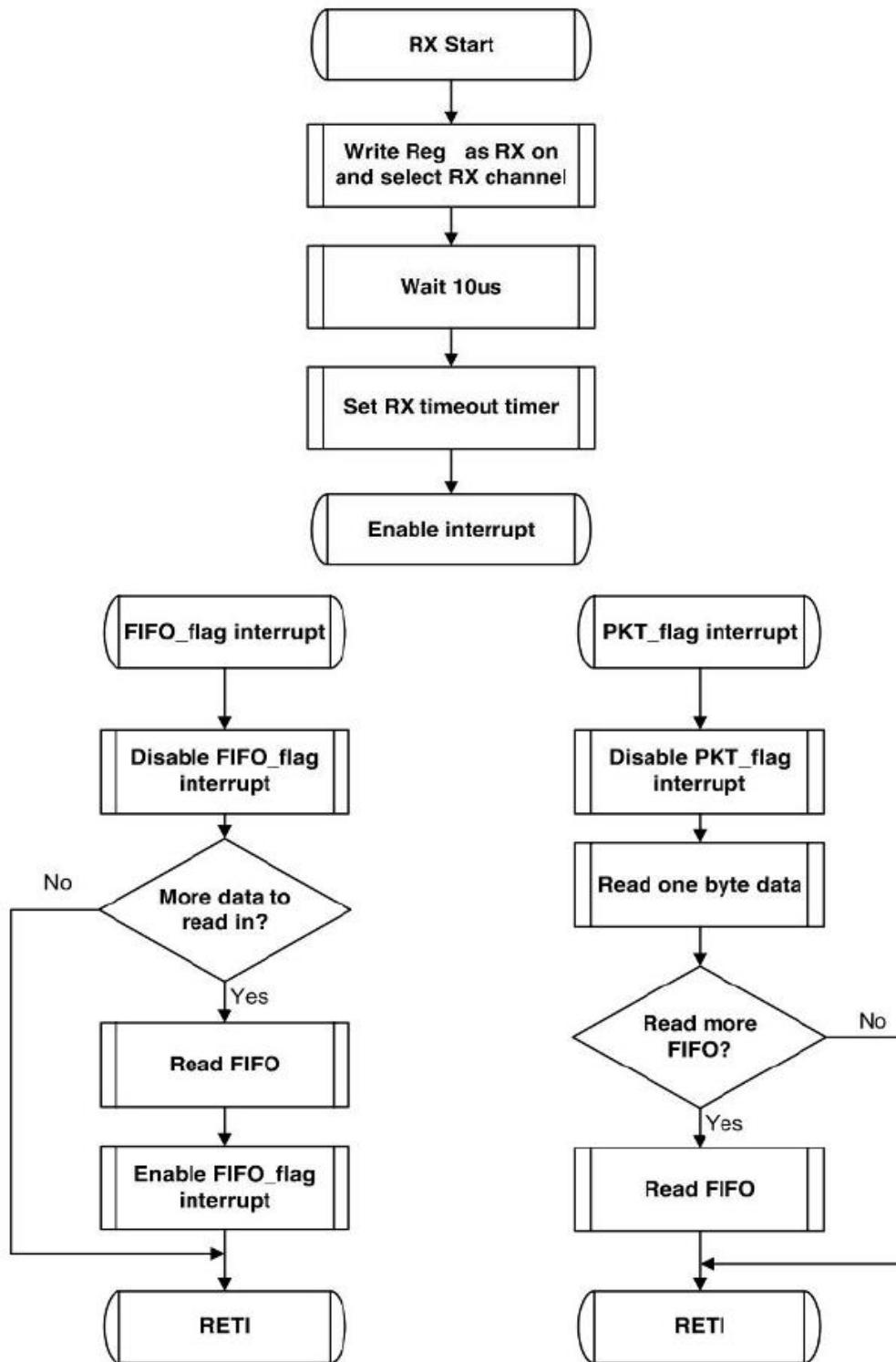

### ◆接收時序

下面顯示 RX 接收時序。當 MCU 將寄存器 0x00[14]寫為 1 並且選擇好接收器通道，晶片將打開 RX 並等待正確的 syncword。當收到正確的 syncword，晶片將自動開始處理資料包。當資料包處理完畢，狀態機將進入 IDLE。

當接收到的資料包長度長於 63 bytes，FIFO flag 將起作用，意味著 MCU 必須從 FIFO 中讀取數據。

在弱信號、多徑和遠距離時，不一定能收到正確的 syncword。為了避免出現死機情況，MCU 需要做一個計時器。在大多數應用中，資料包是在一定時間視窗內可以收到的，如果沒收到系統要有計時器恢復到正常模式。

接收時序圖

接收流程圖

///////// 接收流程例子：

1. 初始化寄存器，即寫入需要優化的寄存器值

```

write reg[0x0a] = 0x2053;

write reg[0x02] = 0x4060;

write reg[0x05] = 0x7fa6;

write reg[0x0f] = 0x661d;

write reg[0x0d] = 0x6003;

write reg[0x1a] = 0x00f7;

```

2. 清空接收 FIFO

```

write reg[0x25] = 0x8080;

```

4. 啟動接收使能，同時設置頻道

```

write reg[0x00] = 0x40XX; //低 7 位元為頻道號

```

5. 等待 pkt\_flag(reg0x16[16])為高，表示接收到一幀資料，開始從接收 FIFO 讀數據,讀出的第一個位元組為資料長度

read reg[0x28]

### ◆自動回應和自動重傳

該功能可配置的寄存器有：

寫寄存器 0x01[3] = 1, 使能 auto-ack 功能

寫寄存器 0x0b[11:8], 設置重發次數，預設值是 3，即第一次發送失敗後，再重發 2 次

寫寄存器 0x0b[5:0], 設置等待 ACK 時間，默認是 0x3f，每個 step 是 16us，總共大約為 1ms，

表示等待 1ms 時間沒收到 ACK 包且重發次數沒有到最大值就會重新發送資料包。

使能和不使能 AUTO-ACK 功能的區別在於 pkt\_flag 的拉起時間不一樣：

發射方等待收到 ACK 包後或未收到 ACK 包重發次數已最大，這時會拉起 pkt\_flag，退出發射狀態，mcu 在 pkt\_flag 拉高後，可讀寄存器 0x16[7]位，如果為 1 即收到 ACK 包。

接收方在收到資料包後再發出 ACK 包，然後退出接收狀態，拉起 pkt\_flag 信號。

ACK 包的時間約為 150us，這由 preamble 和 syncword 的長度決定。

### ◆CRC16 校驗

該功能默認為開啟。

寫寄存器 0x01[13]開啟或關閉 CRC 功能。

CRC 開啟但 AUTO-ACK 功能沒有開啟時，晶片接收狀態不受 CRC 狀態影響，但寄存器會有 CRC error 狀態位元。pkt\_flag 拉起後，mcu 可讀 0x16[15]位判斷 CRC 是否正確，決定是否需要讀該幀資料。

CRC 開啟且 AUTO-ACK 功能開啟，這時晶片會自動判斷 CRC 是否正確，如果接收方 pkt\_flag 拉起，說明收到一幀資料包且 CRC 正確。

### 應用層決定包長度

當寄存器 0x01[2]=0 時，payload 第一個位元組沒有特殊意義，包長度由寄存器 0x01[1]決定。

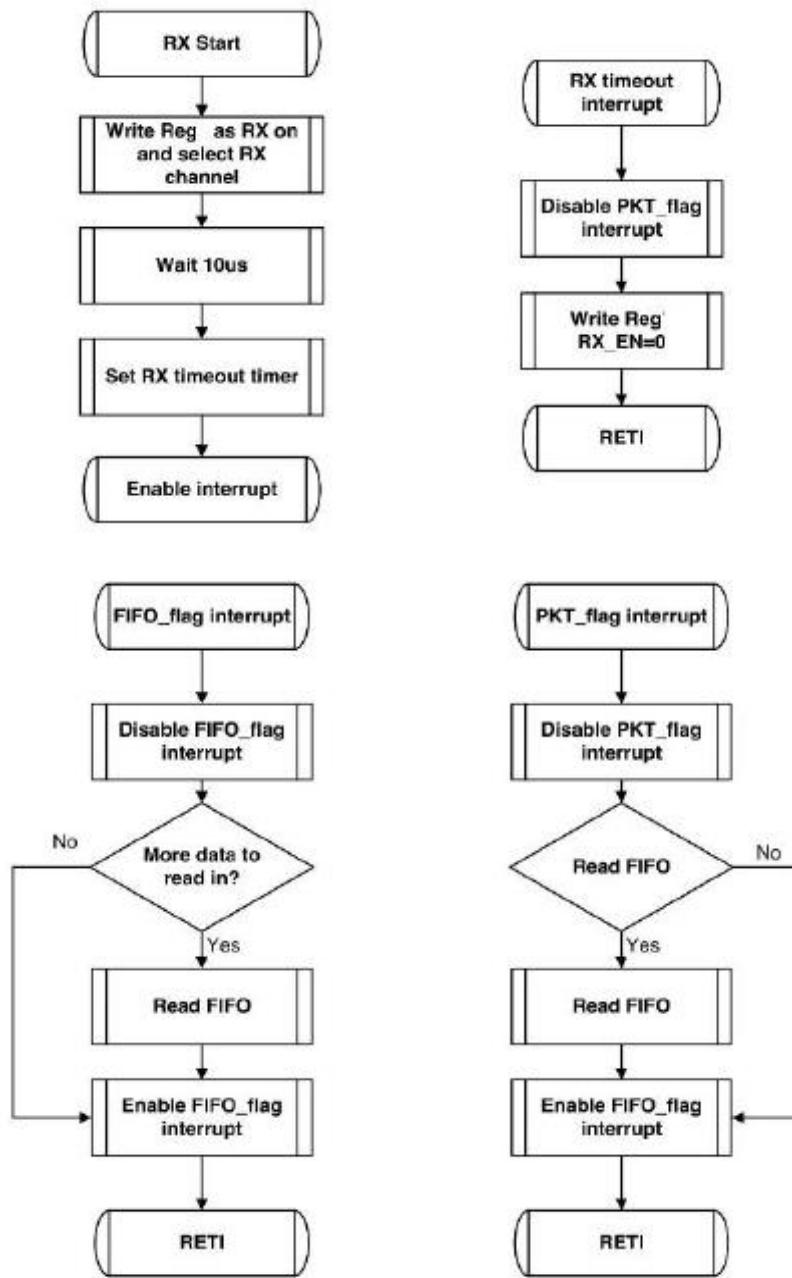

#### ◆fw\_term\_tx=1

當寄存器 0x01[1]=1，在發射資料時，系統將比較發送 FIFO 的寫指針和讀指針，如果 MCU 停止向發送 FIFO 寫資料，晶片將會最終探測到 FIFO 何時為空，然後自動退出發射狀態。

時序圖如下：

注意：當寄存器 0x01[1]=0, 不要讓 FIFO 過空或過滿，FIFO full/empty 閾值可以通過寄存器 FIFO THRESHOLD 設置，最優值由 I2C 速度和 MCU 讀寫 FIFO 速度決定。

using interrupts for PKT and FIFO flags.

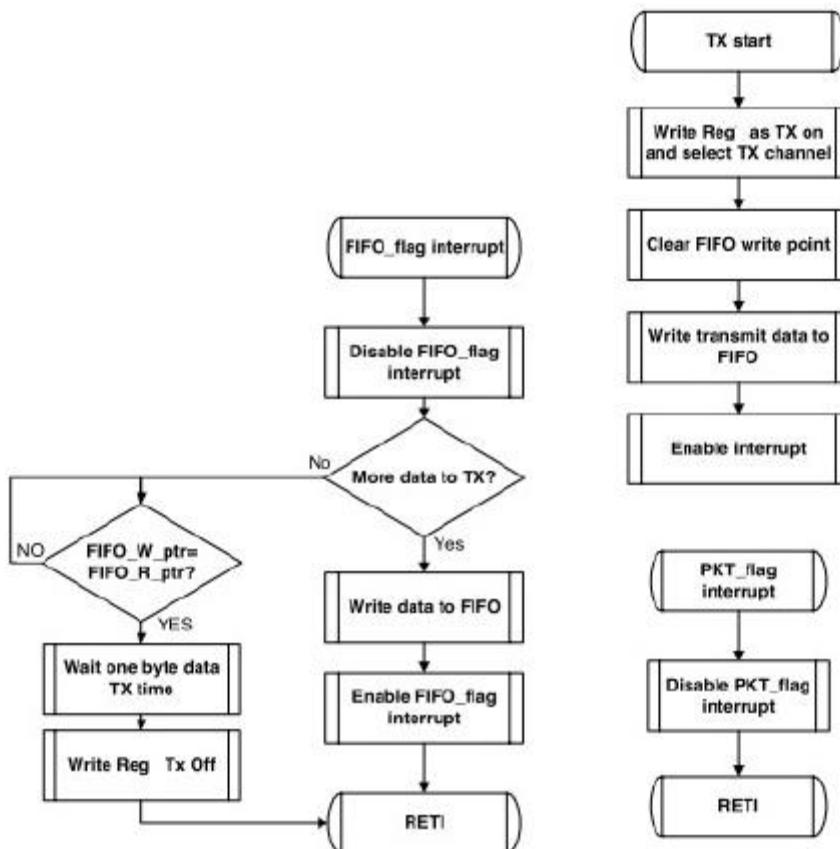

寄存器 0x01[2:1]=2'b01 時發射的流程圖

### ◆fw\_term\_tx=0(TX)

當寄存器 0x01[2:1]=2'b00 時，系統只有在寄存器 0x00[15] tx\_en=0 時停止發射。

當寄存器 0x01[2:1]=2'b00 時，TX 時序圖

using interrupts for PKT and FIFO flags.

當寄存器 0x01[2:1]=2'b00 時，TX 流程圖

#### ◆fw\_term\_tx=0 (RX)

當 Reg0x01[2]=0 時，晶片將會在 Reg0x00[14] RX\_EN=1 時開始接收包，此時晶片將會自動將 RX 設定到固定的頻道接收。在等待一定時間使內部時鐘和 RX 電路穩定後，晶片開始在收到的信號中尋找 syncword。一旦找到，將拉高 PKT flag，並向 FIFO 裡寫收到的資料。PKT flag 將一直為高直到 MCU 將 FIFO 中的資料讀完。當 MCU 把數據讀完後，PKT flag 將拉低直到下個 TX/RX 週期。

當 Reg0x01[2:1]= 'b00 or 'b01 時，必須由 MCU 將 Reg0x00[14] 寫為 0 才能退出 RX 狀態。

當 Reg0x01[2:1]= 'b00 or 'b01 時，RX 時序圖

using interrupts for PKT and FIFO flags.

當 Reg0x01[2:1]='b00 or 'b01 時，RX 流程圖

## PA 輸出功率設置

PA 的輸出功率可以通過寄存器 PA\_PW\_SET[3:0]，即 reg0x02[3:0]來設置，reg0x02[3:0]是一個無符號數，數值越大，PA 輸出功率越小。最大輸出功率可到 6dBm 左右，對應 reg0x02[3:0]=0000，最小輸出功率約為 -18dBm 左右，對應 reg0x02[3:0]=1111。

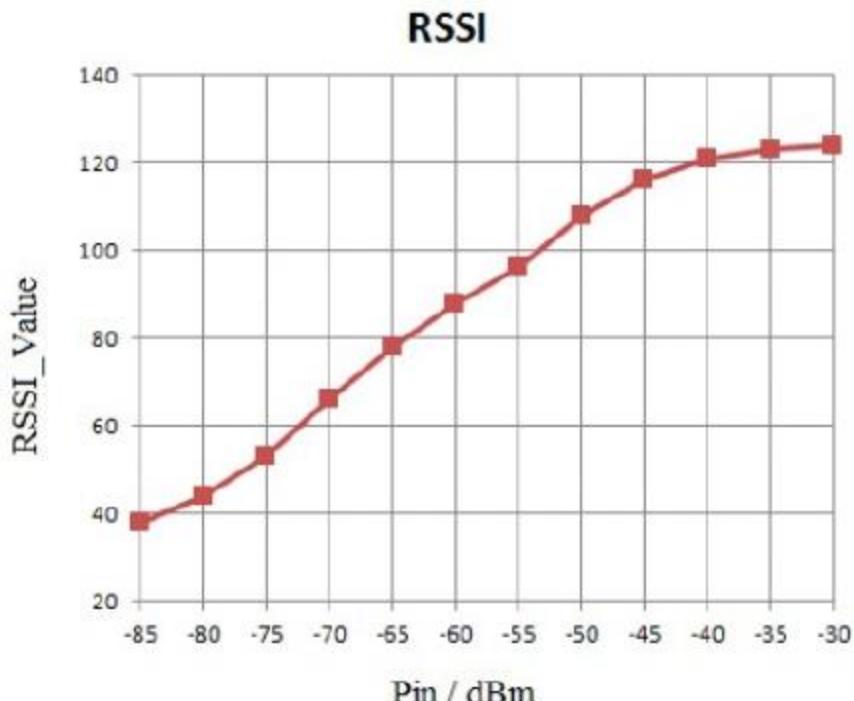

## RSSI

支援 RSSI 檢測功能，在 RX 狀態下，可通過 reg0x11[15:8]直接讀取即時的 RSSI 值，其檢測方法如下：

(1) 將晶片設置在 RX 狀態；

(2) 先將 reg0x1c[15]寫為 1，關閉 RSSI 以消除之前留存的 RSSI 值。然後再將 reg0x1c[15]寫為 0，開啟 RSSI 檢測功能，等待 60us 之後就可以通過 reg0x11[15:8]讀取當下的 RSSI 值。

下圖是晶片 RSSI 檢測功能的實測性能：