### Description

The EJW5052C is a current mode monolithic buck voltage converter. Operating with an input range of 4.5V-18V, The EJW5052C delivers 2A of continuous output current with two integrated N-Channel MOSFETs. At light loads, regulators operate in low frequency to maintain high efficiency and low output ripple. The EJW5052C guarantees robustness with short circuit protection, thermal protection, current run-away protection, and input under voltage lockout. The EJW5052C is available in a 6-pin SOT23-6 package, which provides a compact solution with minimal external components.

### **Features**

- ◆4.5V to 18V operating input range

- A output current

- ♦Up to 93% efficiency

- ◆High efficiency at light load

- ◆Fixed 700kHz Switching frequency

- Input under voltage lockout

- Start-up current run-away protection

- Over current protection and Hiccup

- Thermal protection

- Available in SOT23-6 package

### **Applications**

- Distributed Power Systems

- Networking Systems

- ◆FPGA, DSP, ASIC Power Supplies

- Green Electronics/ Appliances

- Notebook Computers

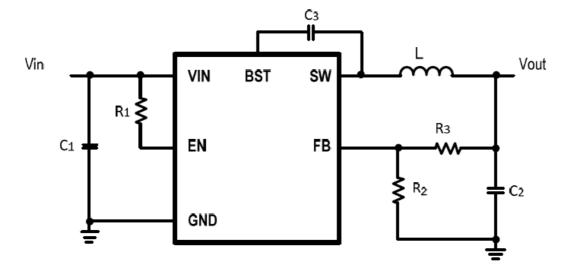

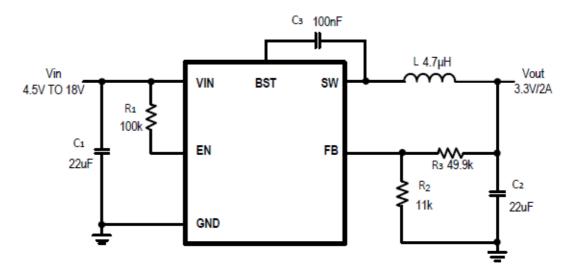

# **Typical application**

# 2A Step Down Regulator

# Ordering/Marking Information

EJW5052C XX X X Package Type : B3 : SOT23-6 F : Pb Free G : Green

| Device       | Marking        | Package | Information                                                                                        |

|--------------|----------------|---------|----------------------------------------------------------------------------------------------------|

| EJW5052CB3XR | JWH6X<br>YWLLL | SOT23-6 | H6 : Product code<br>X : Assembly House Code<br>Y : Year Code<br>W : Week Code<br>LLL : Lot number |

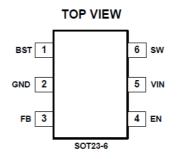

# **Pin Configurations**

# Absolute Maximum Ratings<sup>1)</sup>

| VIN, EN Pin >        | -0.3V to 20V                              |

|----------------------|-------------------------------------------|

|                      | 0.3V(-4.5V for 10ns) to 20V(22V for 10ns) |

| BST Pin              | ŚW-0.3V to SW+5V                          |

| All other Pins       | -0.3V to 6V                               |

| Junction Temp. 2) 3) |                                           |

| Lead Temperature     |                                           |

|                      |                                           |

# **Recommended Operating Conditions**

| Input Voltage VIN     | . 4.5V to 18V |

|-----------------------|---------------|

| Output Voltage Vout0. | 6V to VIN-3V  |

# Thermal Performance<sup>4)</sup>

| SOT23-6 | . 220130ºC/W |

|---------|--------------|

Note :

Exceeding these ratings may damage the device.

2) The EJW5052C guarantees robust performance from -40°C to 150°C junction temperature. The junction temperature range specification is assured by design, characterization and correlation with statistical process controls.

3) The EJW5052C includes thermal protection that is intended to protect the device in overload conditions. Thermal protection is active when junction temperature exceeds the maximum operating junction temperature. Continuous operation over the specified absolute maximum operating junction temperature may damage the device.

4) Measured on JESD51-7, 4-layer PCB

E-CMOS Corp. (www.ecmos.com.tw)

$\theta_{JA}$

$\theta_{JC}$

### **Electrical Characteristics** VIN=12V, TA=25°C Unless otherwise stated

| Item                                                | Symbol                   | Conditions                                                         | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------|--------------------------|--------------------------------------------------------------------|------|------|------|------|

| VIN Under Voltage Lock-out Threshold                | V <sub>IN_MIN</sub>      | V <sub>IN</sub> rising                                             | 3.85 | 4.2  | 4.45 | V    |

| VIN Under voltage Lockout Hysteresis <sup>5</sup> ) | V <sub>IN_MIN_HYST</sub> |                                                                    |      | 300  |      | mV   |

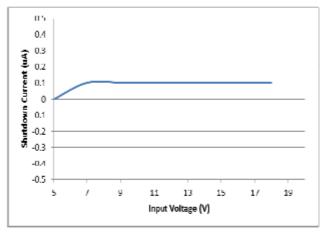

| Shutdown Supply Current                             | I <sub>SD</sub>          | V <sub>EN</sub> =0V                                                |      | 0.1  | 1    | μA   |

| Supply Current                                      | Ι <sub>Q</sub>           | V <sub>EN</sub> =5V, V <sub>FB</sub> =1.2V                         |      | 100  | 130  | μA   |

| Feedback Voltage                                    | V <sub>FB</sub>          | 4.5V <v<sub>VIN&lt;18V</v<sub>                                     | 588  | 600  | 612  | mV   |

| Top Switch Resistance <sup>5)</sup>                 | R <sub>DS(ON)T</sub>     |                                                                    |      | 130  |      | m    |

| Bottom Switch Resistance <sup>5)</sup>              | R <sub>DS(ON)B</sub>     |                                                                    |      | 70   |      | m    |

| Top Switch Leakage Current                          | I <sub>LEAK_TOP</sub>    | V <sub>IN</sub> =18V, V <sub>EN</sub> =0V,<br>V <sub>SW</sub> =0V  |      | 0.1  | 1    | μA   |

| Bottom Switch Leakage Current                       | I <sub>LEAK_BOT</sub>    | V <sub>IN</sub> =18V, V <sub>E</sub> N=0V,<br>V <sub>SW</sub> =18V |      | 0.1  | 1    | μA   |

| Top Switch Current Limit <sup>5)</sup>              | I <sub>LIM_TOP</sub>     | Minimum Duty<br>Cycle                                              | 3.2  | 3.9  | 4.6  | Α    |

| Switch Frequency                                    | F <sub>SW</sub>          |                                                                    | 560  | 700  | 800  | kHz  |

| Minimum On Time <sup>5)</sup>                       | T <sub>ON_MIN</sub>      |                                                                    |      | 120  |      | ns   |

| Minimum Off Time <sup>5</sup> )                     | T <sub>OFF_MIN</sub>     | V <sub>FB</sub> =0.4V                                              |      | 150  |      | ns   |

| EN high level input voltage                         | V <sub>EN_H</sub>        | V <sub>EN</sub> rising                                             | 1.45 |      |      | V    |

| EN low level input voltage                          | V <sub>EN_L</sub>        | V <sub>EN</sub> falling                                            |      |      | 0.6  | V    |

| Thermal Shutdown <sup>5</sup> )                     | T <sub>TSD</sub>         |                                                                    |      | 150  |      | °C   |

| Thermal Shutdown hysteresis <sup>5</sup> )          | T <sub>TSD_HYST</sub>    |                                                                    |      | 20   |      | °C   |

Note :

5) Guaranteed by design.

### **Pin Description**

| Pin | Name | Description                                                                                                                                                                           |  |  |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | BST  | Bootstrap pin for top switch. A 0.1uF or larger capacitor should be connected between this pin and the SW pin to supply current to the top switch and top switch driver.              |  |  |

| 2   | GND  | Ground.                                                                                                                                                                               |  |  |

| 3   | FB   | Output feedback pin. FB senses the output voltage and is regulated by the control loop to 0.6V. Connect a resistive divider at FB.                                                    |  |  |

| 4   | EN   | Drive EN pin high to turn on the regulator and low to turn off the regulator.                                                                                                         |  |  |

| 5   | VIN  | Input voltage pin. VIN supplies power to the IC. Connect a 4.5V to 18V supply to VIN and bypass VIN to GND with a suitably large capacitor to eliminate noise on the input to the IC. |  |  |

| 6   | SW   | SW is the switching node that supplies power to the output. Connect the output LC filter from SW to the output load.                                                                  |  |  |

EJW5052C

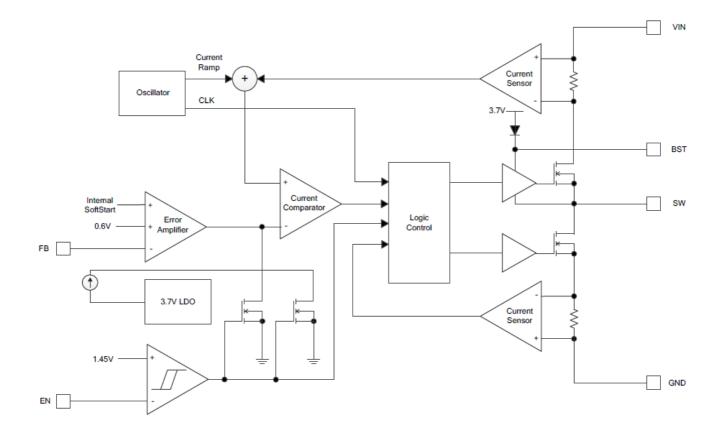

# **Block Diagram**

### **Typical Performance Characteristics**

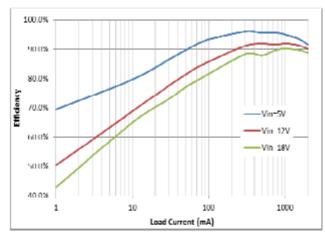

### Vin =12V, Vout = 3.3V, L = $4.7\mu$ H, Cout = $22\mu$ F, TA = $+25^{\circ}$ C, unless otherwise noted

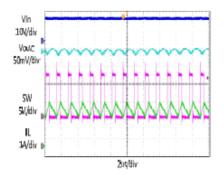

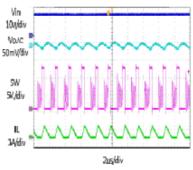

### Steady State Test

VIN=12V, Vout=3.3V lout=2A

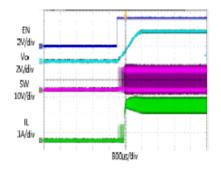

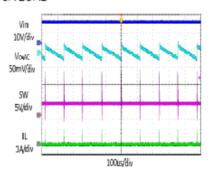

#### Startup through Enable VIN=12V, Vout=3.3V

Iout=2A(Resistive load)

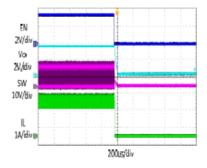

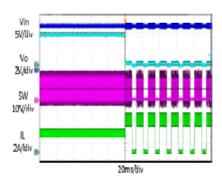

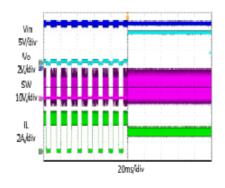

Shutdown through Enable

VIN=12V, Vout=3.3V Iout=2A (Resistive load)

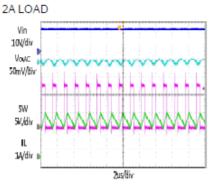

Heavy Load Operation

# Medium Load Operation

0.2A LOAD

# Light Load Operation

### Short Circuit Protection

VIN=12V, Vout=3.3V Iout=2A- Short

### Short Circuit Recovery

VIN=12V, Vout=3.3V Iout= Short-2A

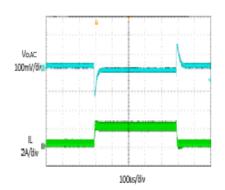

### Load Transient

$0.2A \text{ LOAD} \rightarrow 2A \text{ LOAD} \rightarrow 0.2A \text{ LOAD}$

### EJW5052C

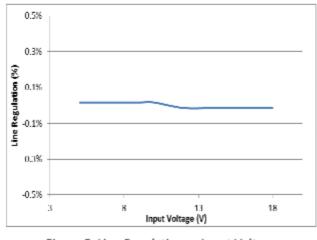

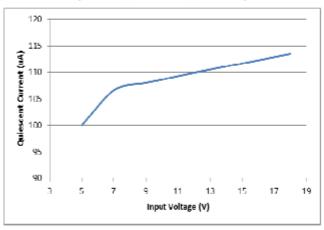

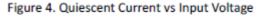

### Vin =12V, Vout = 3.3V, L = 4.7µH, Cout = 22µF, TA = +25°C, unless otherwise noted

Figure 1. Efficiency vs Load Current

Figure 5. Line Regulation vs Input Voltage

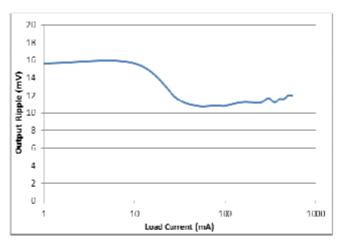

Figure 2. Output Ripple vs Load Current

(Vin=12V, Vout=3.3V, L=4.7uH)

(Vout=3.3V, L=4.7uH)

(Vout=3.3V, L=4.7uH)

### **Functional Description**

The EJW5052C is a synchronous, current-mode, step-down regulator. It regulates input voltages from 4.5V to 18V down to an output voltage as low as 0.6V, and is capable of supplying up to 2A of load current.

### **Current-Mode Control**

The EJW5052C utilizes current-mode control to regulate the FB voltage. Voltage at the FB pin is regulated at 0.6V so that by connecting an appropriate resistive divider between VOUT and GND, designed output voltage can be achieved.

### PFM Mode

The EJW5052C operates in PFM mode at light load. In PFM mode, switch frequency decreases when load current drops to boost power efficiency at light load by reducing switch-loss, while switch frequency increases when load current rises, minimizing output voltage ripples.

#### Internal Soft-Start.

Soft-Start makes output voltage rising smoothly follow an internal SS voltage until SS voltage is higher than the internal reference voltage. It can prevent overshoot of output voltage when startup.

### **Power Switch**

N-Channel MOSFET switches are integrated on the EJW5052C to down convert the input voltage to the regulated output voltage. Since the top MOSFET needs a gate voltage greater than the input voltage, a boost capacitor connected between BST and SW pins is required to drive the gate of the top switch. The boost capacitor is charged by the internal 3.7V rail when SW is low.

#### Vin Under-Voltage Protection

A resistive divider can be connected between Vin and GND, with the central tap connected to EN, so that when Vin drops to the pre-set value, EN drops below 1.2V to trigger input under voltage lockout protection.

#### **Output Current Run-Away Protection**

At start-up, due to the high voltage at input and low voltage at output, current inertia of the output inductance can be easily built up, resulting in a large start-up output current. A valley current limit is designed in the EJW5052C so that only when output current drops below the valley current limit can the top power switch be turned on. By such control mechanism, the output current at start-up is well controlled.

### **Over Current Protection and Hiccup**

EJW5052C has a cycle-by-cycle current limit. When the inductor current triggers current limit, EJW5052C enters hiccup mode and periodically restart the chip. EJW5052C exits hiccup mode while not triggering current limit.

#### **Thermal Protection**

When the temperature of the EJW5052C rises above 150°C, it is forced into thermal shut-down. Only when core temperature drops below 135°C can the regulator becomes active again.

### **Application Information**

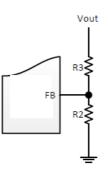

### **Output Voltage Set**

The output voltage is determined by the resistor divider connected at the FB pin, and the voltage ratio is:

$$v_{FB} = v_{OUT} \cdot \frac{R_2}{R_2 + R_3}$$

where VFB is the feedback voltage and VOUT is the output voltage. Choose R2 around 10kM, and then R3 can be calculated by:

$$R_3 = R_2 \left(\frac{V_{OUT}}{0.6V} - 1\right)$$

Too large resistance and the following table lists the recommended values.

| Vout(V) | R2(kΩ) | R3(kΩ) |

|---------|--------|--------|

| 2.5     | 10     | 31.6   |

| 3.3     | 11     | 49.9   |

| 5       | 15     | 110    |

### **Input Capacitor**

The input capacitor is used to supply the AC input current to the step-down converter and maintaining the DC input voltage. The ripple current through the input capacitor can be calculated by:

$$I_{C1} = I_{LOAD} \cdot \sqrt{\frac{V_{OUT}}{V_{IN}}} \cdot \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

where  $I_{\text{LOAD}}$  is the load current,  $V_{\text{OUT}}$  is the output voltage,  $V_{\text{IN}}$  is the input voltage.

Thus the input capacitor can be calculated by the following equation when the input ripple voltage is determined.

$$C_{1} = \frac{I_{\text{LOAD}}}{f_{\text{S}} \cdot \Delta V_{\text{IN}}} \cdot \frac{V_{\text{OUT}}}{V_{\text{IN}}} \cdot \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)$$

where C1 is the input capacitance value, fs is the switching frequency,  $\triangle$ VIN is the input ripple voltage.

The input capacitor can be electrolytic, tantalum or ceramic. To minimizing the potential noise, a small X5R or X7R ceramic capacitor, i.e. 0.1uF, should be placed as close to the IC as possible when using electrolytic capacitors.

A 22uF ceramic capacitor is recommended in typical application.

#### **Output Capacitor**

The output capacitor is required to maintain the DC output voltage, and the capacitance value determines the output ripple voltage. The output voltage ripple can be calculated by:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_s \cdot L} \cdot \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \cdot \left(R_{ESR} + \frac{1}{8 \cdot f_s \cdot C_2}\right)$$

where C2 is the output capacitance value and RESR is the equivalent series resistance value of the output capacitor.

The output capacitor can be low ESR electrolytic, tantalum or ceramic, which lower ESR capacitors get lower output ripple voltage. The output capacitors also affect the system stability and transient response, and a 22uF ceramic capacitor is recommended in typical application.

#### Inductor

The inductor is used to supply constant current to the output load, and the value determines the ripple current which affect the efficiency and the output voltage ripple. The ripple current is typically allowed to be 40% of the maximum switch current limit, thus the inductance value can be calculated by:

$$L = \frac{V_{OUT}}{f_{s} \cdot \Delta I_{L}} \cdot \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

where  $V_{IN}$  is the input voltage,  $V_{OUT}$  is the output voltage, fs is the switching frequency, and  $\triangle I_L$  is the peak-to-peak inductor ripple current.

### **External Bootstrap Capacitor**

A bootstrap capacitor is required to supply voltage to the top switch driver. A 0.1uF low ESR ceramic capacitor is recommended to connected to the BST pin and SW pin.

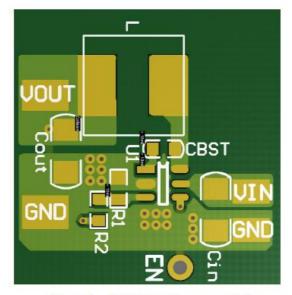

### **PCB Layout Note**

For minimum noise problem and best operating performance, the PCB is preferred to following the guidelines as reference.

1. Place the input decoupling capacitor as close to eJW5052C (VIN pin and PGND) as possible to eliminate noise at the input pin. The loop area formed by input capacitor and GND must be minimized.

2. Put the feedback trace as far away from the inductor and noisy power traces as possible.

3. The ground plane on the PCB should be as large as possible for better heat dissipation.

# 3A, 40V Asynchronous Step-Down Converter

EJW5052C

Figure 1. PCB Layout Recommendation

### **External Components Suggestion**

| Vout(V) | R2 (kΩ) | R3 (kΩ) | L(uH)   | Cout(uF) |

|---------|---------|---------|---------|----------|

| 1       | 10.2    | 6.8     | 3.3~4.7 | 44~66    |

| 1.2     | 10.2    | 10.2    | 3.3~4.7 | 44~66    |

| 1.5     | 10      | 15      | 3.3~4.7 | 44~66    |

| 2.5     | 10      | 31.6    | 3.3~4.7 | 22~66    |

| 3.3     | 11      | 49.9    | 4.7     | 22~66    |

| 5       | 15      | 110     | 4.7     | 22~66    |

### **Reference Design**

# Reference 1

- V<sub>IN</sub> : 4.5V ~ 18V

- V<sub>OUT</sub>: 3.3V

- I<sub>OUT</sub>: 0~2A

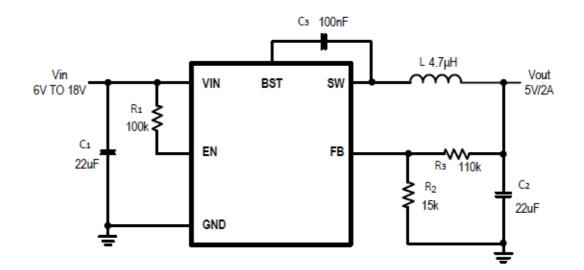

# Reference 2

V<sub>IN</sub> : 6V ~ 18V V<sub>OUT</sub>: 5V I<sub>OUT</sub>: 0~2A

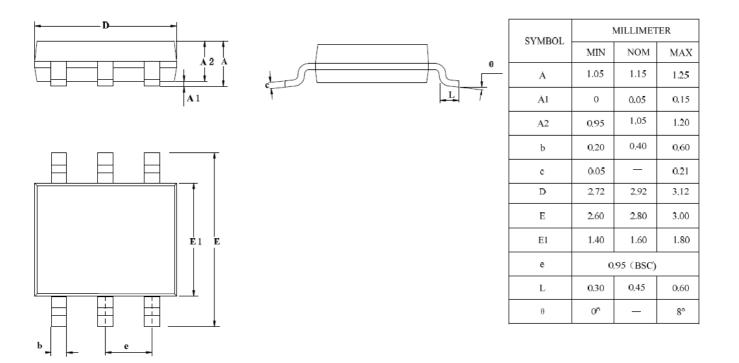

Package Outline SOT23-6

UNIT: mm