#### **ECK1815CA**

#### **Features**

- ♦650V E-Mode GaN integrated Gate Driver

- ♦170mΩ RDS ON

- ♦Wide input range with hysteresis

- ◆Wide Vcc range (10V~30V)

- ◆Fast and controllable rise time and fall time

- ◆Zero reverse recovery loss

- ◆Small DFN 5x6 package

DFN 5x6

#### **Applications**

- ◆AC-DC Adapter

- **◆**DC-DC Converter

- **♦**LED Lighting

- ◆Power Factor Correction

- ◆Charger

Circuit Symbol

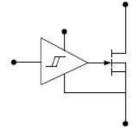

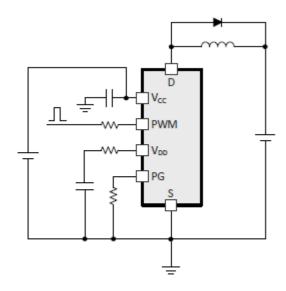

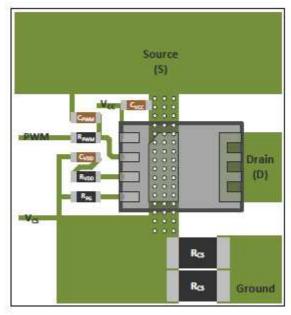

## **Typical Application Circuit**

## **Marking Information**

- (A) Part Number

- (B) Date Code (Year: 2 digits / Weak: 2 digits)

- (C) Internal Code (3 digits)

# **Pin Configurations**

## **Pin Assignment**

| Pin No. | Symbol          | Description                                                      |

|---------|-----------------|------------------------------------------------------------------|

| 1       | V <sub>cc</sub> | Supply voltage.                                                  |

| 2       | PWM             | PWM input.                                                       |

| 3       | $V_{DD}$        | Gate driver supply voltage. Gate driver turn-on current set pin. |

| 4       | PG              | Power Ground. Gate driver turn-off current set pin.              |

| 5/6/7/8 | D               | Drain of GaN HEMT.                                               |

| E-PAD   | S               | Source of GaN HEMT and Gate Driver ground.                       |

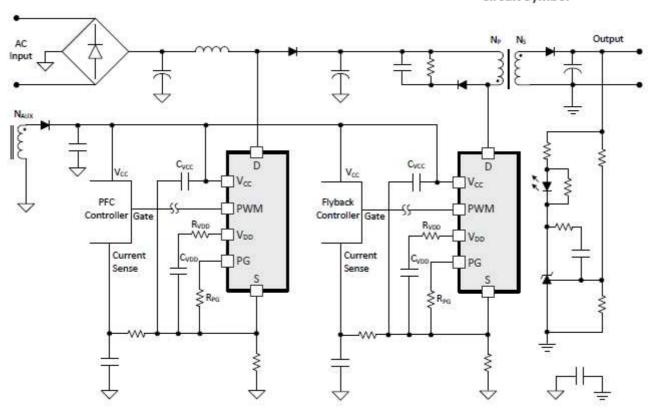

## **Block Diagram**

**Absolute Maximum Ratings**

| Symbol               | Parameter                                                   | Rating         |

|----------------------|-------------------------------------------------------------|----------------|

| V <sub>DS_TRAN</sub> | Transient Drain to Source Voltage (Pulse ≤ 1us)             | 800V           |

| V <sub>DS</sub>      | Continuous Drain to Source Voltage                          | 650V           |

| V <sub>CC</sub>      | Supply Voltage                                              | 30V            |

| V <sub>PWM</sub>     | PWM Pin Voltage                                             | -3V to 30V     |

| I <sub>D</sub>       | Continuous Drain Current @ T <sub>C</sub> =100°C            | 8A             |

|                      | Pulsed Drain Current (Pulse = 10us) @ T <sub>C</sub> =25°C  | 16A            |

| I <sub>DP</sub>      | Pulsed Drain Current (Pulse = 10us) @ T <sub>C</sub> =125°C | 12A            |

| dV/dt                | Slew Rate on Drain to Source                                | 200V/ns        |

| Tı                   | Operating Junction Temperature                              | -55°C to 150°C |

| T <sub>STG</sub>     | Storage Temperature                                         | -55°C to 150°C |

- These are stress ratings only and functional operation is not implied. Exposure to absolute maximum ratings for prolonged time periods may affect device reliability.

- All voltages are with respect to ground.

**Recommended Operating Conditions**

| Symbol           | Parameter                                          | Min | Тур | Max | Unit |

|------------------|----------------------------------------------------|-----|-----|-----|------|

| V <sub>cc</sub>  | Supply Voltage                                     | 10  |     | 24  | V    |

| V <sub>PWM</sub> | PWM input Voltage (Do not exceed V <sub>CC</sub> ) | 0   | 5   | 20  | V    |

| T <sub>C</sub>   | Operating Case Temperature                         | -40 |     | 125 | °C   |

- These are conditions under which the device functions but the specifications might not be guaranteed.

- For guaranteed specifications and test conditions, please see the Electrical Specifications.

**Package Information**

| Symbol        | Parameter                                | Rating | Unit |

|---------------|------------------------------------------|--------|------|

| $\theta_{JC}$ | Thermal Resistance (Junction to Case)    | 2      | °C/W |

| $\theta_{JA}$ | Thermal Resistance (Junction to Ambient) | 38     | °C/W |

• Thermal resistance is measured on FR4 PCB of 1 square inch 2oz Cu.

# **GaN HEMT integrated Gate Driver**

**ECK1815CA**

## **Electrical Characteristics**

| Symbol                 | 20V, F <sub>SW</sub> =1MHz, R <sub>TR</sub> =10Ω, T <sub>A</sub> =25°C, unles<br>Parameter | Test Condition                                                     | Min  | Тур  | Max  | Unit |  |  |

|------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------|------|------|------|--|--|

| V <sub>cc</sub> Specif | V <sub>CC</sub> Specifications                                                             |                                                                    |      |      |      |      |  |  |

| IQ                     | V <sub>CC</sub> Quiescent Current                                                          | V <sub>PWM</sub> =0V                                               |      | 0.06 | 1.5  | mA   |  |  |

| I <sub>cc</sub>        | V <sub>CC</sub> Operating Current                                                          | F <sub>SW</sub> =1MHz, V <sub>DS</sub> =OPEN                       |      | 1.1  |      | mA   |  |  |

| V <sub>DD</sub> Speci  | fications                                                                                  |                                                                    |      |      |      |      |  |  |

| $V_{DD}$               | V <sub>DD</sub> Operating Voltage                                                          |                                                                    | 4.5  | 5.2  | 5.9  | V    |  |  |

| PWM Log                | cic Input Specifications                                                                   |                                                                    | •    |      |      |      |  |  |

| $V_{PWMH}$             | PWM Input High Threshold                                                                   |                                                                    |      |      | 1.4  | V    |  |  |

| $V_{PWML}$             | PWM Input Low Threshold                                                                    |                                                                    | 1.1  |      |      | V    |  |  |

| $V_{\text{PWM\_HYS}}$  | PWM Input Hysteresis                                                                       |                                                                    |      | 0.3  |      | V    |  |  |

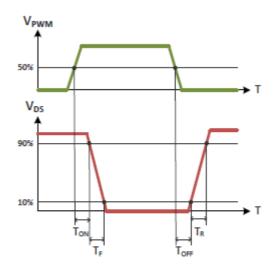

| T <sub>ON</sub>        | Turn-on Propagation Delay                                                                  | Fig. 1, 2                                                          |      | 3    |      | ns   |  |  |

| T <sub>OFF</sub>       | Turn-off Propagation Delay                                                                 | Fig. 1, 2                                                          |      | 4    |      | ns   |  |  |

| T <sub>R</sub>         | V <sub>DS</sub> Rise Time                                                                  | Fig. 1, 2                                                          |      | 7    |      | ns   |  |  |

| T <sub>F</sub>         | V <sub>DS</sub> Fall Time                                                                  | Fig. 1, 2                                                          |      | 4    |      | ns   |  |  |

| Switching              | s Specifications                                                                           |                                                                    | •    |      |      |      |  |  |

| $F_{SW}$               | Switching Frequency                                                                        |                                                                    |      |      | 2    | MHz  |  |  |

| $T_PW$                 | Pulse Width                                                                                |                                                                    | 0.02 |      | 1000 | us   |  |  |

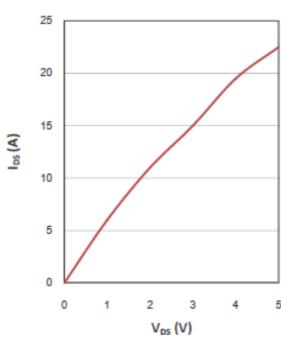

| GaN Spec               | GaN Specifications                                                                         |                                                                    |      |      |      |      |  |  |

|                        | Durin Course Losland Course                                                                | V <sub>PWM</sub> =0V, V <sub>DS</sub> =650V                        |      | 2    | 20   | uA   |  |  |

| I <sub>DSS</sub>       | Drain-Source Leakage Current                                                               | V <sub>PWM</sub> =0V, V <sub>DS</sub> =650V, T <sub>J</sub> =150°C |      | 10   | 120  | uA   |  |  |

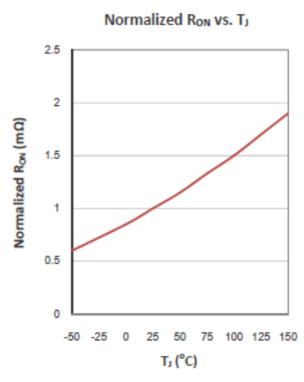

| D                      | Drain-Source Resistance                                                                    | I <sub>D</sub> =3A                                                 |      | 170  | 260  | mΩ   |  |  |

| R <sub>DSON</sub>      |                                                                                            | I <sub>D</sub> =3A, T <sub>J</sub> =150°C                          |      | 320  |      | mΩ   |  |  |

| $V_{SD}$               | Source-Drain Reverse Voltage                                                               | V <sub>PWM</sub> =0V, I <sub>SD</sub> =2A                          |      | 2.7  |      | V    |  |  |

# **GaN HEMT integrated Gate Driver**

#### **ECK1815CA**

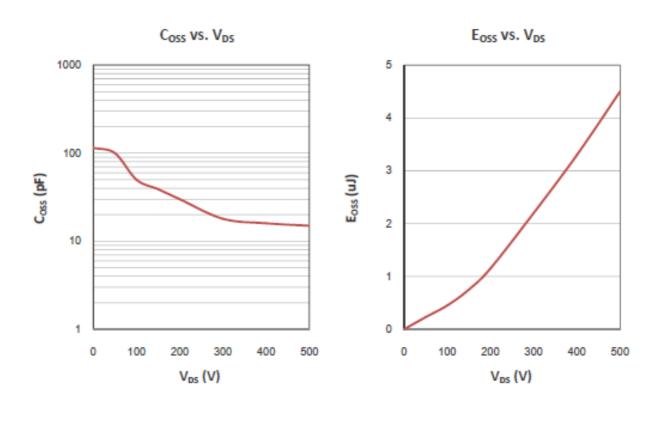

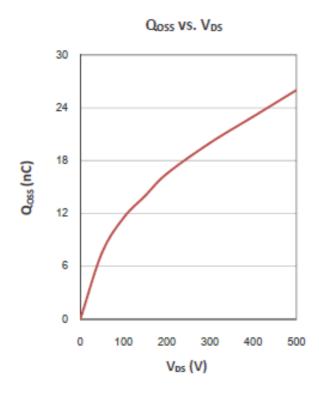

| Q <sub>oss</sub>   | Output Charge                                   | V <sub>PWM</sub> =0V, V <sub>DS</sub> =400V       | 19 | nC |

|--------------------|-------------------------------------------------|---------------------------------------------------|----|----|

| Q <sub>RR</sub>    | Reverse Recovery Charge                         |                                                   | 0  | nC |

| C <sub>OSS</sub>   | Output Capacitance                              | V <sub>PWM</sub> =0V, V <sub>DS</sub> =400V       | 20 | pF |

| C <sub>O(ER)</sub> | Effective Output Capacitance,<br>Energy Related | V <sub>PWM</sub> =0V, V <sub>DS</sub> =0V to 400V | 27 | pF |

| C <sub>O(TR)</sub> | Effective Output Capacitance,<br>Time Related   | V <sub>PWM</sub> =0V, V <sub>DS</sub> =0V to 400V | 43 | pF |

<sup>•</sup>  $C_{O(ER)}$  is the fixed capacitance that would give the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 V to the stated  $V_{DS}$ .  $C_{O(TR)}$  is the fixed capacitance that would give the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 V to the stated  $V_{DS}$ .

#### **Test Circuits**

Fig. 1

Inductive switching circuit

Fig. 2

Propagation delay & rise/fall time definitions

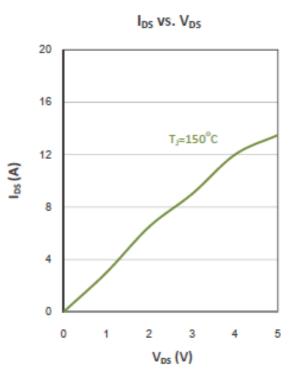

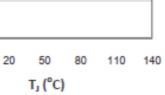

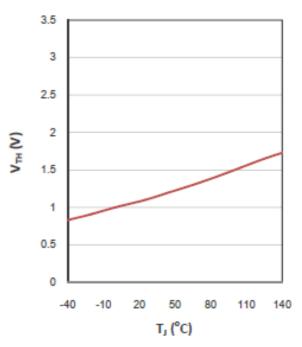

## **Typical Performance Characteristics**

3.5

1

0.5

0

-40

## V<sub>PWMH</sub> vs. Temperature

# 3 2.5 2 2 1.5

## V<sub>PWML</sub> vs. Temperature

-10

**ECK1815CA**

#### **Application Information**

#### **Normal Operation**

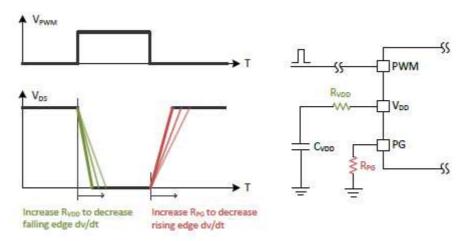

When VCC pin is given a suggestion voltage (10~24V), the internal circuit blocks are active, and the VDD will be set at 5.2V by internal voltage regulator. The internal gate drive detects the PWM signal and according as the PWM voltage level to turn-on/off the GaN HEMT, and the dv/dt slew rate can be set by an external resistor on VDD pin or PG pin. It is useful to optimize the overall efficiency and EMI.

#### V<sub>DS</sub> dv/dt Control

Connect an external resistor ( $R_{VDD}$ ) between  $V_{DD}$  pin and  $C_{VDD}$  can set the gate driver current that will change the  $V_{DS}$  fall time. The  $V_{DS}$  rise time can be set by an external resistor ( $R_{PG}$ ) on PG pin. The following figure shows the  $V_{DS}$  dv/dt change with respect to  $R_{VDD}$  and  $R_{PG}$ .

$R_{VDD}$  must be used by minimum  $10\Omega$  to ensure application and device robustness.

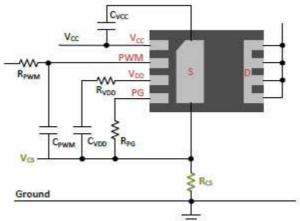

#### **PWM RC Filter**

To prevent the false triggering, an external RC filter can be inserted between the PWM signal and PWM pin to inhibit the high frequency spike and noise. The typical value is  $100\Omega/100$ pF.

#### **Current Sensing**

Many applications need to sense the current flowing through the power device. A typical connection is placing a current sensing resistor between the Source pin (S) and ground. In this configuration, all of the components around this power device should be grounded to the Source pin (S).

#### **Recommended Component Values**

The following table shows the recommended component values for the external  $C_{VCC}$ ,  $R_{PWM}$ ,  $C_{PWM}$ ,  $R_{VDD}$ ,  $C_{VDD}$ , and  $R_{PG}$ . These components should be placed as close as possible to the power device. For more layout information, please see the following <u>PCB Layout</u> section.

| Symbol           | Parameter                                 | Min | Тур  | Max | Unit |

|------------------|-------------------------------------------|-----|------|-----|------|

| C <sub>VCC</sub> | V <sub>CC</sub> capacitor                 |     | 0.1  |     | uF   |

| C <sub>VDD</sub> | V <sub>DD</sub> capacitor                 |     | 0.01 |     | uF   |

| R <sub>VDD</sub> | Gate driver turn-on current set resistor  | 10  | 25   |     | Ω    |

| R <sub>PG</sub>  | Gate driver turn-off current set resistor |     | 0    |     | Ω    |

| R <sub>PWM</sub> | PWM filter resistor                       |     | 100  |     | Ω    |

| C <sub>PWM</sub> | PWM filter capacitor                      |     | 100  |     | pF   |

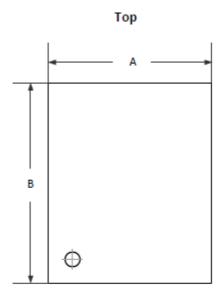

#### **PCB Layout**

The design of PCB layout is very important, especially for the switching power supply of high frequency and large peak current. A good layout minimizes EMI on the switching note and current path, and reduces the temperature of power device. The following layout guides can be used to ensure the power device proper operation.

- (1). All of the components around the power device should be placed as close as possible, including  $C_{VCC}$ ,  $R_{PWM}$ ,  $C_{PWM}$ ,  $R_{VDD}$ ,  $C_{VDD}$ , and  $R_{PG}$ .

- (2). Place thermal vias in the source pad to conduct the heat out through the bottom of package and throughthe PCB to the other layers.

- (3). For high power density design, use large thermal plane connecting with thermal vias to the source pad and additional PCB layers as much as possible. It is useful to reduce the temperature of power device.

Recommended PCB Layout (Top)

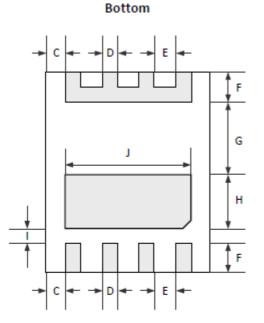

Recommended PCB Layout (Bottom)

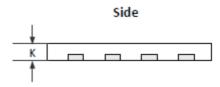

# Package Information DFN 5x6

| Symbol | Dimension (mm) |       |       |  |  |  |

|--------|----------------|-------|-------|--|--|--|

| Symbol | Min.           | Тур.  | Max.  |  |  |  |

| А      | 4.9            | 5     | 5.1   |  |  |  |

| В      | 5.9            | 6     | 6.1   |  |  |  |

| С      | 0.245          | 0.345 | 0.445 |  |  |  |

| D      | 0.4            | 0.5   | 0.6   |  |  |  |

| E      | 0.67           | 0.77  | 0.87  |  |  |  |

| F      | 0.6            | 0.7   | 0.8   |  |  |  |

| G      | 1.8            | 1.9   | 2     |  |  |  |

| Н      | 2.1            | 2.2   | 2.3   |  |  |  |

| I      | 0.4            | 0.5   | 0.6   |  |  |  |

| J      | 4.2            | 4.3   | 4.4   |  |  |  |

| К      | 0.75           | 0.85  | 0.95  |  |  |  |